多波形雷達回波中頻模擬器設計

3.2 數字噪聲基帶產生模塊

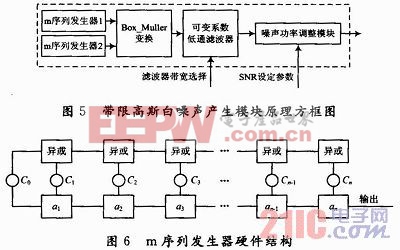

本系統噪聲基帶信號的產生采用數字技術,在FPGA內完成,實現方法如圖5所示。本文引用地址:http://www.104case.com/article/187411.htm

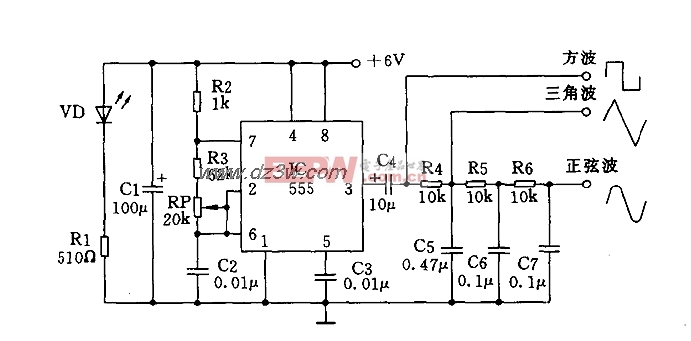

根據隨機信號理論,對均勻分布的隨機數進行白化處理,可實現具有良好統計特性的高斯白噪聲。系統首先采用2個獨立的m序列發生器產生[0,1]區間上均勻分布的偽隨機數,m序列發生器的硬件結構如圖6所示,其中Co和Cn為對應m序列多項式的系數,取值為0和1。

然后將產生的一對偽隨機數通過Box_Muller變換可以得到一對相互獨立的符合標準正態分布的偽隨機數m和n,正好作為噪聲產生器的同相分量和正交分量。Box_Muller變換公式為:

式中:x,y即為前述2個互相獨立的在(0,1)上均勻分布的偽隨機數。

由于Box_Muller變換需要用到兩個非線性函數 和cos 2πy,而非線性運算很難在實際數字電路系統中實現,故實際中需要構建相應查找表實現非線性運算,分別記作sqrt_lut和sincos_lut。設sqrt_lut和sincos_Iut的輸出量化數據長度為L1和L2位,獨立變量m和n的定點長度分別為N1和N2位。則當采用均勻量化方案時,sqrt_lut和sincos_lut所需的存儲空間分別為2N1×L1和2N2×L2。可以看出,如果直接實現查找表功能,當N1和N2較大時,對應的存儲空間是相當可觀的。

和cos 2πy,而非線性運算很難在實際數字電路系統中實現,故實際中需要構建相應查找表實現非線性運算,分別記作sqrt_lut和sincos_lut。設sqrt_lut和sincos_Iut的輸出量化數據長度為L1和L2位,獨立變量m和n的定點長度分別為N1和N2位。則當采用均勻量化方案時,sqrt_lut和sincos_lut所需的存儲空間分別為2N1×L1和2N2×L2。可以看出,如果直接實現查找表功能,當N1和N2較大時,對應的存儲空間是相當可觀的。

為了壓縮存儲空間,對sincos_lut,可以只存儲第一象限的正余弦值。其他象限則通過符號調整得到,這樣可以將sincos_lut占用存儲空間減少到原來的1/4。更進一步,還可以對非線性曲線進行分段折線近似,在實際查找表中只存儲各折線段的起始位置及對應斜率。也可以大幅度減少所需查找表的數量,該策略同樣適用于sqrt_lut查找表。

得到一對相互獨立的符合標準正態分布變量m和n后,還要對其進行低通濾波,以適應對應的信號帶寬。由于I路與Q路的濾波特性完全相同,為進一步節省資源,可采用一個支持雙通道操作的濾波器同時完成I路與Q路的濾波。這可以通過ISE集成開發環境中Core Generator中的FIR IP核來方便實現。濾波器系統可由上位機根據所需帶寬,傳遞相應系數給DSP,繼而傳遞給FPGA。

噪聲功率調整模塊可根據設定信噪比的不同,乘以相應系數,對產生的帶限高斯白噪聲幅度進行調整。

4 結論

本系統基于自主產生的原理,選用DSP和FPGA為核心處理器,通過合理的算法設計,實現了可兼容多種雷達波形的中頻雷達回波模擬器的設計,采用改進的基于存儲轉發的數字脈沖延時方法,在達到8 ns的最小延時步長的同時,降低了對系統的硬件要求。系統的另一個關鍵模塊是數字噪聲發生器,其參數可以進行實時修改,極大地提高了噪聲發生器的靈活性,與其他同類型設計相比,具有工作速度快,資源利用率高,硬件結構簡單等特點。最后采用DDS、數字正交上變頻等器件,實現了精確的復雜頻率調制、相位調制和幅度調制,保證了系統的靈活性、高兼容性和集成化程度。

評論