基于FPGA+DSP的雷達回波發生器設計

采用DSP和FPGA/CPLD相結合的系統結構綜合了兩者在系統控制和實時數字信號處理方面的優勢,結構靈活、實現性強[1]。本文提出了一種以FPGA為核心,DSP實時控制,外加PROM、Flash、CPLD以及D/A等外圍電路構成的雷達中頻回波信號發生器的設計方法,可以通過在線編程在相同的硬件平臺上實現不同體制、多目標的雷達回波。

1 雷達回波發生器方案設計

1.1 系統性能要求

本雷達回波發生器是為了對雷達信號處理機進行測試、評估以及新的信號處理算法而開發研制的,因而在設計上要滿足通用性要求,能模擬產生不同體制雷達的回波信號[2]。通用性設計要求硬件外圍接口電路盡可能簡單,對各種電平規范具有兼容性;所選器件適應性強,通過重配置可編程邏輯電路即可產生不同帶寬、不同時寬的雷達信號而不用修改硬件設計[3-4]。同時,為了真實地反映雷達目標的復雜環境,要求雷達回波發生器能加入噪聲和干擾,從而能夠對信號處理機進行全面的評估和檢測。

本雷達回波發生器要求能選擇產生單脈沖跟蹤、DBF、SAR 3種體制雷達的最多3個目標的回波信號,雷達波形為簡單脈沖、線性調頻信號、相位編碼信號可選。主要技術指標如下:

(1)中頻載頻頻率:30 MHz;

(2)系統基準時鐘:10 MHz;

(3)波形存儲深度為10 K,信號采樣率100 MHz;

(4)幅度分辨率為12 bit;

(5)頻率范圍為0.37 Hz~25 MHz,頻率分辨率為0.37 Hz;

(6)輸出模擬信號幅度范圍為±2.5 V;

(7)DBF體制時天線陣元數為16個。

1.2 系統實現方案

雷達回波發生器的實現有以下3種方法:全硬件實現、微機+D/A插卡實現以及微機+模擬器DSP組合實現。由于全硬件實現時硬件設計過于復雜、靈活性差、微機+D/A插卡方法受D/A數據傳輸率的限制,所以目前雷達回波發生器的設計中,多采用微機+模擬器DSP組合方法。該方法靈活性好、數據量適中、易擴充、滿足通用性要求[5]。

通過對幾種回波發生器實現方法的比較,結合本雷達回波發生器要實現的功能以及靈活性、通用性的設計思想,本文提出了一種新的雷達中頻回波發生器的設計與實現方法。該方法嚴格說仍屬于微機+模擬器DSP組合方法,但采用了微機+FPGA+DSP+D/A的組合,如圖1所示。

與傳統的雷達回波發生器實現方法相比,采用該結構具有以下優點:

(1)PC機不必實時為回波發生器提供數據,只是在雷達參數改變時,PC機才給存儲器輸入新的波形和參數數據。這樣便能采用更為逼真的雷達回波數學模型,并能對這些模型完成更為復雜和精確的處理工作,提高模擬信號環境的逼真性;

(2)硬件實現簡單,只要改變底層軟件而不用更改硬件電路就可以適應不同體制的雷達,因而這種方法具有較好的靈活性和通用性;

(3)對外具有豐富的接口,既可以當作一塊獨立的板卡使用,也可以在CPCI機箱上作為標準板卡使用;

(4)利用其豐富的底層軟件庫,可以提供良好的二次開發空間。

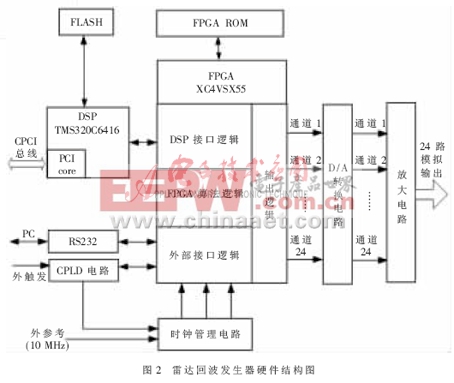

2 系統硬件設計

雷達回波發生器在硬件實現時,FPGA選用Xilinx公司Virtex-4系列的XC4VSX55芯片, DSP選用TI公司的TMS320C6416芯片,數模轉換器和放大器分別選用ADI公司的AD9765和AD8044,時鐘選用ADI公司的超低抖動時鐘ICAD9510,時鐘配置電路選用Altera公司MAX7000S/AE系列的EPM7128S。SX55是Xilinx公司的一款高性能數字信號處理FPGA,具有強大的數據處理能力。主要硬件資源為49 152個SLICE(含一個觸發器及一個四輸入查找表),320個BLOCK RAM(每塊18 KB),512個18×18 bit乘法器,8個DCM,32條全局時鐘連線,640個可用I/O。TMS320C6416是TI公司的一款高性能定點數字信號處理器,最高工作時鐘600 MHz,可達4 800 MIPS。主要硬件資源有128 KB L1P cache,128 KB L1D cache,8 MB L2 cache。兩個外部存儲器接口(EMIF),EMIFA為64 bit,EMIFB為16 bit,共1 280 MB外部地址。64個EDMA,32 bit或16 bit HPI接口,PIC接口。雷達回波發生器的硬件結構如圖2所示。

系統的工作流程是:

(1)雷達波形數據的計算產生。通用計算機根據輸入的雷達參數計算得到雷達基帶信號波形數據,以備通過RS-232串行接口傳輸給大容量波形存儲器存儲。

(2)數據傳輸。FPGA通過電平轉換芯片與串口相連,將經RS-232串行接口送來的通用計算機產生的雷達基帶信號數據以及雷達目標、噪聲有關參數接收并存儲在其內部設計的存儲器中。

(3)實時信號處理。FPGA對存儲數據進行延時、多普勒調制、幅度控制、中頻調制以及噪聲加載等信號處理,得到雷達回波的數字信號。當雷達參數或目標屬性、噪聲參數改變時,DSP更新存儲器中存儲的數據。

評論