基于CPLD的三相多波形函數發生器設計

1 引言

直接數字頻率合成 ?Direct Digital Synthesis ,DDS?是20世紀60年代末出現的第三代頻率合成技術。該技術從相位概念出發,以Nyquist時域采樣定理為基礎,在時域中進行頻率合成。DDS頻率轉換速度快,頻率分辨率高,并在頻率轉換時可保持相位的連續,因而易于實現多種調制功能。DDS是全數字化技術,其幅度、相位、頻率均可實現程控,并可通過更換波形數據靈活實現任意波形。此外,DDS易于單片集成,體積小,價格低,功耗小,因此DDS技術近年來得到了飛速發展,其應用也越來越廣泛。

基于CPLD和DDS技術的函數發生器可以實現信號波形的多樣化,而且方便可靠,簡單經濟,系統易于擴展,同時可大大提高輸出信號的帶寬。

2 系統原理

2.1 CPLD內部設計

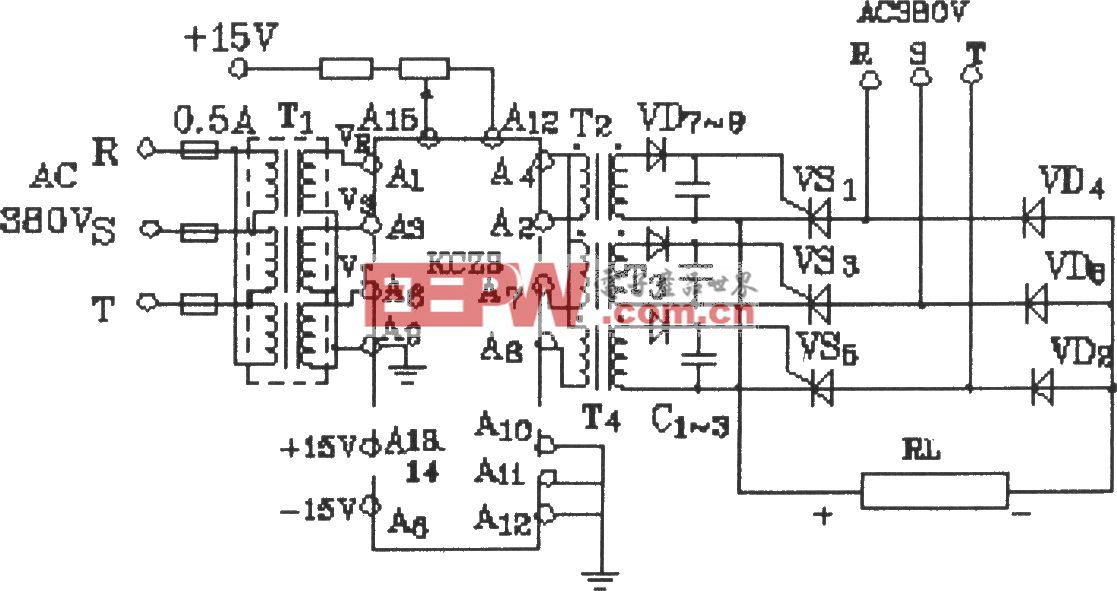

CPLD的內部結構框圖如圖1所示,圖中,首先由控制寄存器將外部控制器(如單片機)送入的數據轉換為頻率和幅度控制字;然后再由分頻器根據頻率控制字進行分頻并將輸出作為尋址計數器的時鐘;尋址計數器的尋址空間為360字節,可對ROM中的查找表進行尋址;而通過模360加法器可以產生120的相位差。

2.2 CPLD的外圍電路

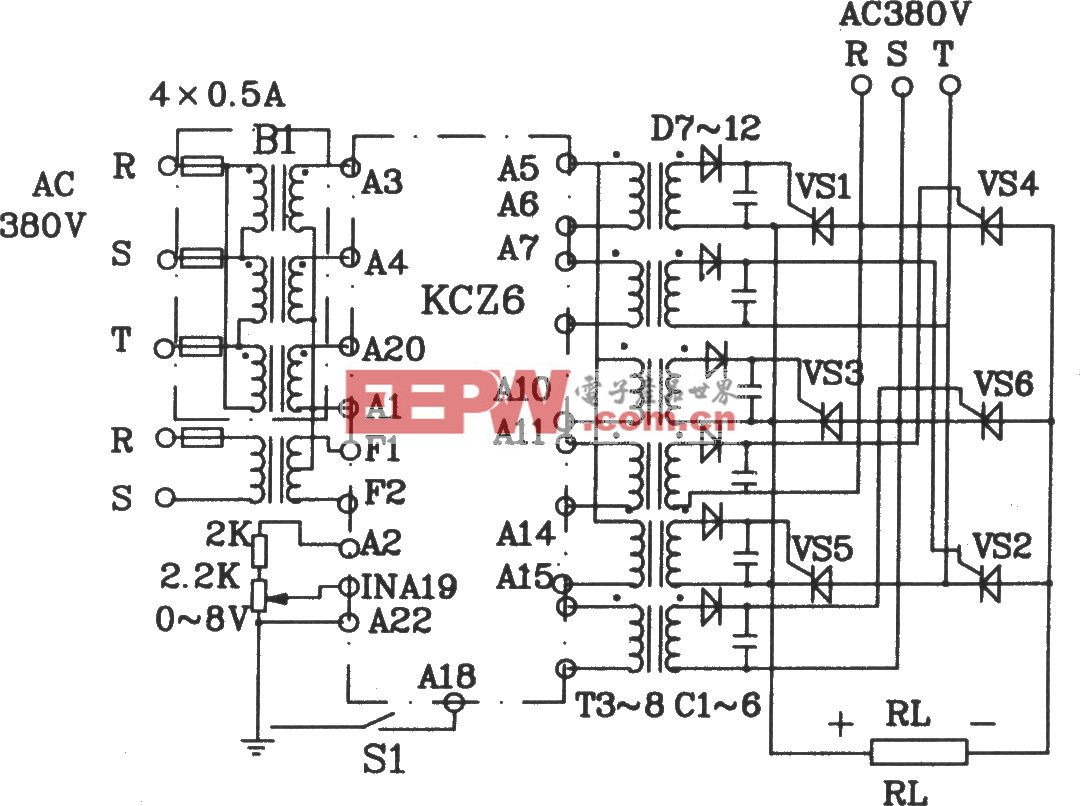

圖2所示是CPLD的外圍電路連接圖。圖中,CPLD幅度控制字經D/A轉換輸出后,可作為查找表輸出DAC的參考電壓,該參考電壓可通過改變幅度控制字來進行改變,從而改變輸出信號的幅度。

3 CPLD各模塊的設計

3.1 控制寄存器的設計

控制寄存器設計主要是將外部控制器輸入的數據轉換為頻率和幅度控制字。其程序代碼如下:

--////////////調庫////////////--

entity controller is

port(clk:in std_logic;

datain:in std_logic;

ad:out std_logic_vector(16 down to 0);

freq:out std_logic_ vector(16 down to 0));

end;

architecture dataflow of controller is

signal out1:std_logic_vector(16 down to 0);

begin

s2p:process(clk,datain)

variable temp:std_logic_vector(16 down to 0);?

begin

if clk'event and clk=‘1’ then

temp:=temp(15 down to 0)&datain;

end if;

out1<=temp;

end process s2p;

mux:process(out1(16))

begin

if out1(16)=‘1’ then

ad<=out1(15 down to 0); --1號寄存器為幅度控制字

else

freq<=out1(15 downto 0); --0號寄存器為頻率控制字

end if;

end process mux;

end;

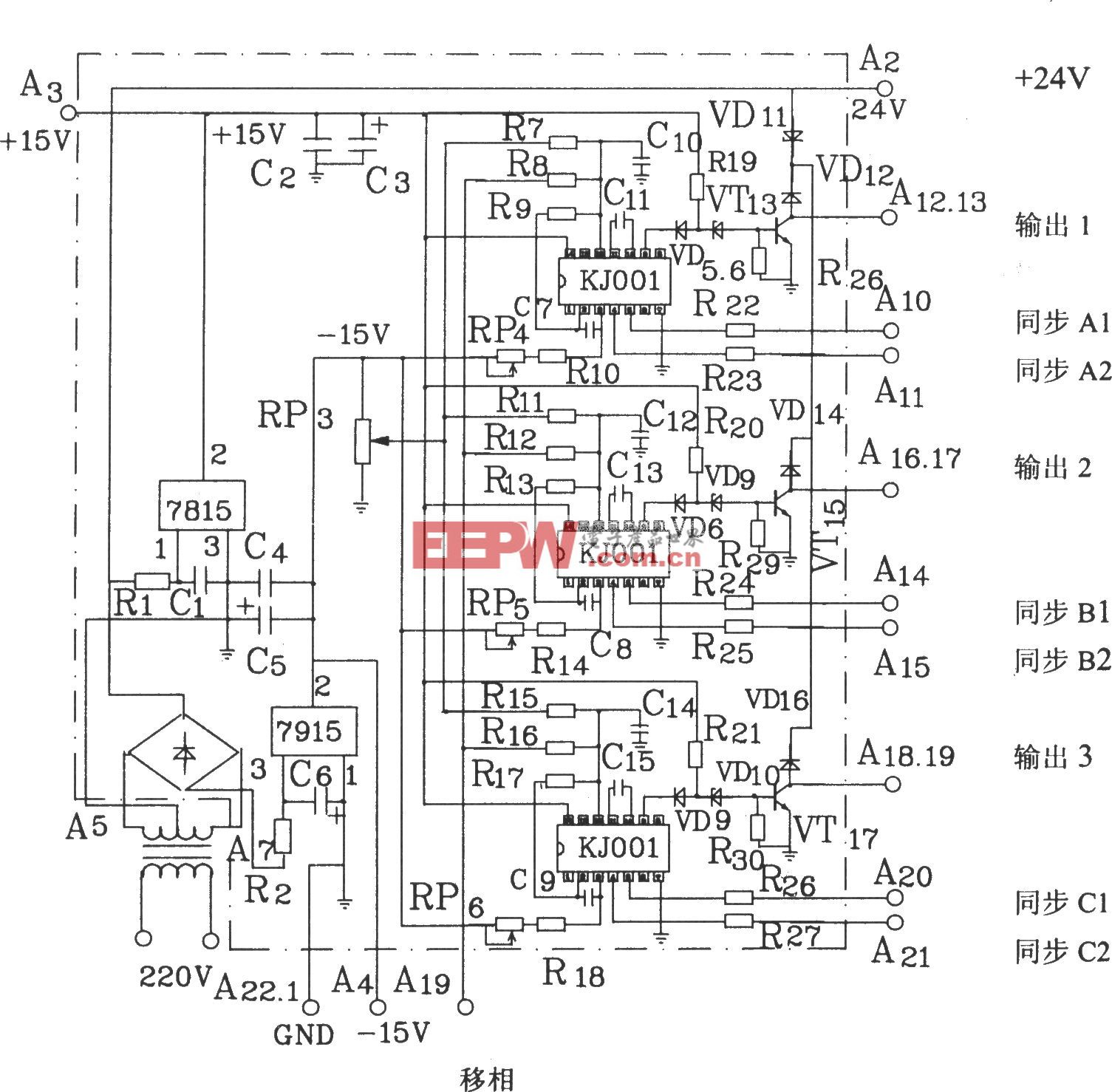

圖3

該設計主要是根據頻率控制字決定分頻倍數,從而輸出與頻率控制字相對應的頻率時鐘,此模塊的輸出可作為尋址計數器的時鐘。具體代碼如下:

process?clk? --clk為外部時鐘(如晶振)

variable temp,fen:std_logic_vector(15 down to 0);?

constant temp1:std_logic_vector(15 down to 0):=“1111111111111111”;

variable a:std_logic;

begin

fen:=temp1-fen_in; --使分頻后的頻率正比于頻率控制字

if clk=‘1’ and clk'event then

if temp=(‘0’&fen(15 down to 1)) then --相當于除2運算

a:=not a;

temp:=temp+1;

elsif temp=fen then

a:=not a;

temp:=“0000000000000000”;

else

temp:=temp+1;

end if;

end if;

fen out<=a; --fen out 為輸入時鐘的頻率fen倍分頻

end process;

3.3 尋址計數器設計

尋址計數器主要用于產生對ROM尋址輸出波形數據的尋址信號,尋址空間為360字節,具體的程序代碼如下:

process(clk)

variable temp:integer range 0 to 359;

begin

if clk=‘1' and clk'event then

if temp<359 then

temp:=temp+1;

else

temp:=0;

end if;

end if;

adress<=temp;

end process;

3.4 模360加法器設計

此模塊用來產生120的相移,以形成三相相差為120的輸出波形。由于尋址空間為360字節,故在輸出尋址數大于360時,須對360取模。程序如下:

process(adress_in)

variable temp?integer range 0 to 511;

begin

temp:=adress in+120;--相移120

if temp<360 then;

adress out<=temp?

else

adress_out<=temp-360;--綜合工具不支持取模運算,故采用減法器來實現

end if;

end process;

3.5 查找表ROM設計

此模塊主要用于存儲各種波形數據,以便通過尋址計數器尋址輸出并經D/A轉換來輸出各種波形,其中包括正弦波、三角波、方波以及鋸齒波。代碼如下:

process(adress,sel)

begin

if sel=“00” then --sel為波形選擇端口,選擇輸出波形,00為正弦波

case adress is

when 000=>data<=0; when 001=>data<=4; ......--正弦波查找表

when others=>null;

end case;

else if sel=“01” then --01輸出方波,

if adress<180 then

data<=255;

else

data<=0;

end if;

else if sel=“10” then --鋸齒波

data<=adress/2;

else --三角波

if adress<180 then

data<=adress;

else

data<=adress-180;

end if;

end if;

end process;

由以上各模塊組成的三相波形發生器原理圖如圖3所示。

4 結束語

此方案可以方便地輸出多種三相波形,而且,由于CPLD具有可編程重置特性,因而可以方便地改變控制方式或更換波形數據,而且簡單易行,易于系統升級,同時具有很高的性價比。

電容式觸摸屏相關文章:電容式觸摸屏原理

評論