24位模數轉換器AD7713及其應用

AD7713的AD公司的24位∑-Δ型模數據轉換,該芯片線性度好,轉換精度高,并具有校準方式多、數據轉換率可程控、功耗低(動態工作方式下的功耗典型值為3.5mW,掉電方式下為35μW)等特點,非常適合于高精度、低功耗數據采集系統的應用。

本文引用地址:http://www.104case.com/article/186233.htmAD7713為24腳DIP結構封裝,有3個模擬輸入通道,其中第1、2兩個通道為差分式輸入,第3通道為單端輸入(可輸入大信號),輸入增益可編程控制(1~128)。AD7713的串行輸出和多種工作方式可以為系統連接提供方便可靠的接口方法。

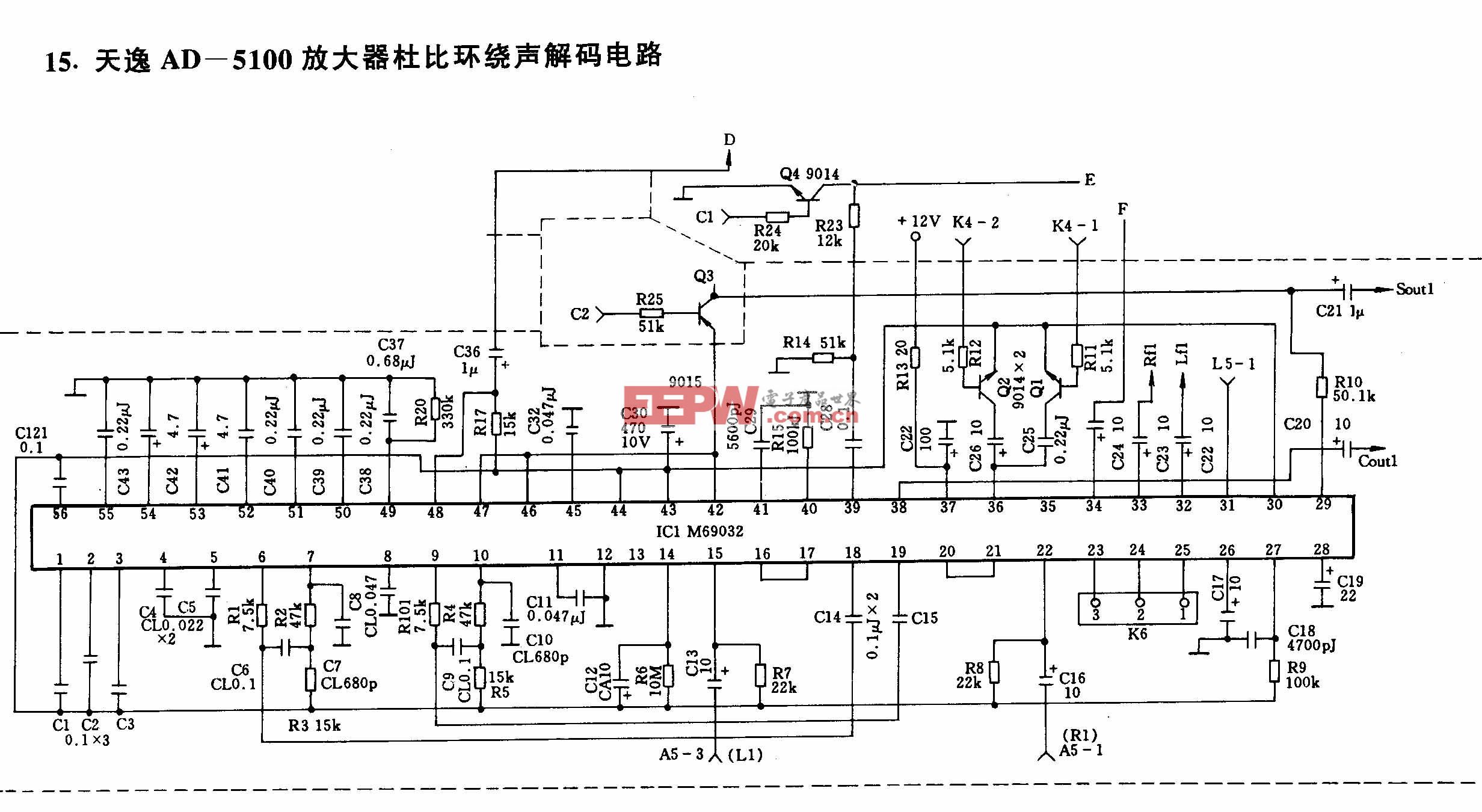

1 AD7713的引腳定義

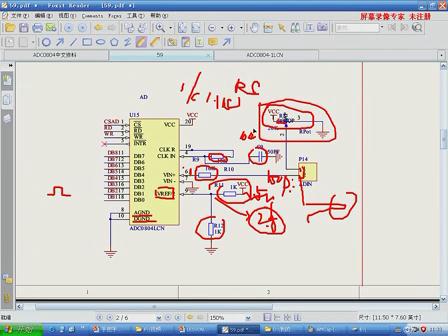

AD7713為大規模集成芯片,其24個引腳(參看圖1)分別定義如下:

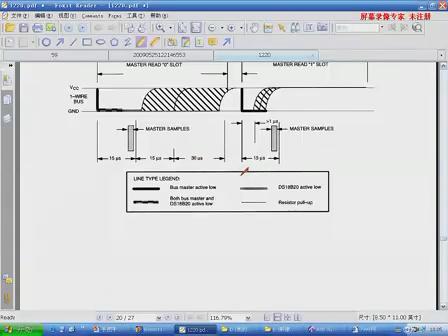

SCLK(1):串行時鐘的輸入/輸出端,可用MODE腳的狀態來控制。當MODE=1時,芯片工作在內部時鐘方式,此時SCLK腳輸出的是一個串行時鐘信號,當RFS或TFS變低時,SCLK被激活;而當RFS或TFS中的一個為高或器件完成一個輸出字的傳送后,SCLK轉為高阻態。當MODE=0時,芯片工作在外部時鐘方式,此時輸入的串行時鐘可用作數據傳送的移位脈沖。

MCLK IN(2):器件的主時鐘信號輸入腳,其主時鐘信號可由石英晶體或外部時鐘提供。使用石英晶體時,石英晶體可直接跨接在MCLK IN和MCLK OUT引腳之間;使用外部時鐘時,該腳可由與CMOS兼容的電平來驅動而將MCLK OUT腳懸空。輸入時鐘的頻率最高為2MHz。

MCLK OUT(3):當主時鐘用石英晶體或陶瓷諧振器時,應將該石英晶體或陶瓷諧振器連接在MCLK IN與MCLK OUT引腳之間。

A0(4):地址輸入,當A0為低時,對器件的控制寄存器進行讀/寫操作;當A0為高時,對器件的數據寄存器或校準寄存器進行讀寫操作。

SYNC(5):邏輯輸入,當系統使用多個AD7713時,使用該引腳可實現各芯片內部數字濾波器的同步。

MODE(6):邏輯輸入,當MODE=1時,器件采用內部時鐘方式;當MODE=0時,器件采用部時鐘方式。

引腳7~10:這四個引腳分別為模擬輸入通道1、2的正、負輸入端。

STANDBY(11):邏輯輸入,當該引腳為低時,將切斷器件內部模擬和數字電路的電源,從而使AD7713處于低功耗狀態。

AVDD(12):模擬正電源,+5~+10V。

RTD1(13):恒流輸出,通常為200μA,可用作電阻式熱敏器件的激勵電流,該電流可由程序來控制通/斷。

REF IN_(14):參考輸入,其電位可取AVDD與AGND之間的任意值。

REF IN+(15):參考輸入,應注意REF IN+,必須在于REF IN-。

RTD2(16):與RTD1腳功能大體相同,也可與RTD1組合使用,另外,利用此腳可在三線RTD結構中消除引線電阻所產生的誤差。

AIN3(17):模擬輸入通道3,輸入信號幅度可達±4VREF/GAIN,當GAIN=1且VREF=2.5V時,AIN3的輸入范圍為±10V。

AGND(18):模擬地。

TFS(19):發送幀同步信號,低電平有效。當TFS=0時,芯片允許寫入串行數據。在內部時鐘方式下,TSF變低將使得串行時鐘SCLK有效;在外部時鐘方式下,TSF必須在數據字被寫入器件的第一個位之前為低。

RFS(20):接收禎同步信號,低RFS=0時,允許對器件進行數據讀取的操作。在內部時鐘方式下,RFS變低將使串行時鐘和數據同時有效;在外部時鐘方式下,RFS變低可使SDATA有效。

DRDY(21):邏輯輸出,表示數據寄存器的更新速率,DRDY的每一個下降沿都將指明一個新的數據字傳輸的開始。當一個完整的數據字傳輸結束后,DRDY將返回到高。

SDATA(22):串行數據。輸入時,CPU將把數據字寫入到器件的控制寄存器或校準寄存器;輸出時,CPU將讀取控制寄存器、校準寄存器、數據寄存器內的數據。

在讀操作期間,RFS變低之后串行數據有效;而在寫操作期,在TFS變低之后,將在SCLK的上升沿加入有效數據。

輸出的數據在單極性輸入時為自然二進制代碼,而在雙極性輸入時為偏移二進制代碼。

DVDD(23):+5V數字電源。DVDD與AVDD的差不得超過0.3V,否則,芯片將不能正常工作。

DGND(24):數字地。

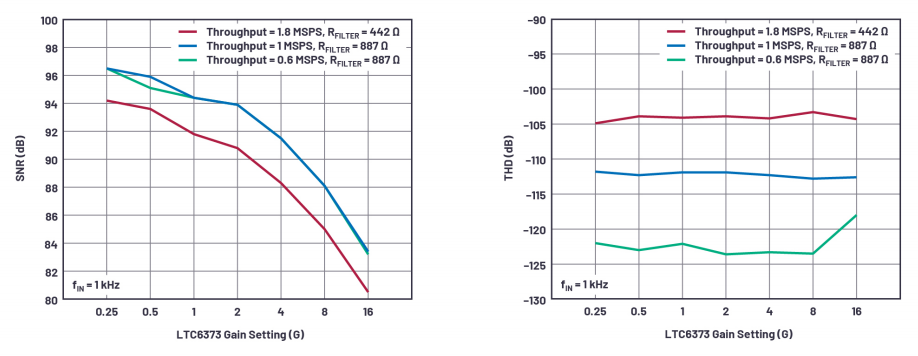

表1 工作方式選擇

MD2 MD1 MD0 工 作 方 式 0 0 0 正常方式,加電復位后的缺省值 0 0 1 自校準有效,用于對激活CH1和CH0所確定的自校準,校準完成后返回正常方式 0 1 0 系統校準有效,對激活通道作第一步系統校準(零點失調校準) 0 1 1 系統校準有效,系統校準的第二步,即滿量程校準 1 0 0 系統失準有效,對激活通道作系統失調校準 1 0 1 背景噪聲校準有產,對激活通道作通道作背景噪聲校準(輸入端與模擬地短接) 1 1 0 讀/寫零點校準系數,當A0=1時,執行讀操作以讀取通道的零點校準系數,同時執行寫操作以寫入零點校準系數 1 1 1 讀/寫滿量程校準系數,當A0=1時,執行讀操作以讀取通道滿量程校準系數,同執行寫操作以寫入滿量程校準系數

表2 通道增益設定

G2 G1 G0 增 益 0 0 0 1(缺省值) 0 0 1 2 0 1 0 4 0 1 1 8 1 0 0 16 1 0 1 32 1 1 0 64 1 1 1 128

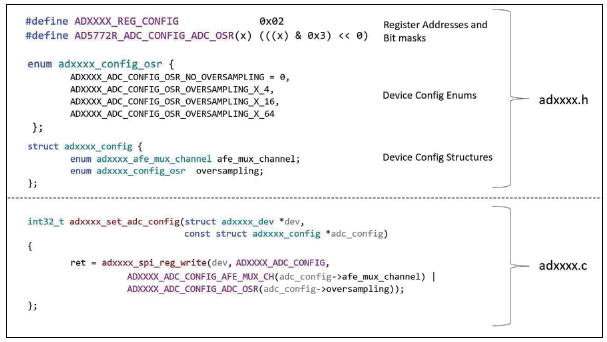

2 AD7713內部控制字的設定

AD7713的工作狀態可通過程序向器件內部寫入控制字來設定,輸入控制字字長為24位。寫入時,必須連續寫入24位數據,若寫入的數據不足,這些數據就不會被加載到控制寄存器中,具體格式為:

格式中的控制字的最高三位用于確定AD7713的工作方式,具體組合如表1所列。G2,G1,G0則用來確定輸入通道的增益,可參見表2。CH1和CH0可確定輸入通道號,其編碼見表3。當字長選擇定義位WL=0時,字長為16位(上電復位時的缺省值);當WL=1時,字長為24位。當激勵電流控制位RO=0時,激勵電流關斷(上電復位時的缺省值);當RO=1時,激勵電流接通。熔斷電流控制(Burn-out Current)定義位BO=0時,關斷AIN端內部的20nA電流源(上電復位時的缺省值);當BO=1時,允許該電流流出,一般情況下,該電流是禁止的。當極性選擇定義位B/U=0時,允許雙極性輸入(上電復位時的缺省值);當B/U=1時,允許單極性輸入。

評論