基于CMOS工藝的高阻抗并行A/D芯片TLC5510

1 概述

本文引用地址:http://www.104case.com/article/186070.htmTLC5510是美國(guó)TI公司生產(chǎn)的新型模數(shù)轉(zhuǎn)換器件(ADC),它是一種采用CMOS工藝制造的8位高阻抗并行A/D芯片,能提供的最小采樣率為20MSPS。由于TLC5510采用了半閃速結(jié)構(gòu)及CMOS工藝,因而大大減少了器件中比較器的數(shù)量,而且在高速轉(zhuǎn)換的同時(shí)能夠保持較低的功耗。在推薦工作條件下,TLC5510的功耗僅為130mW。由于TLC5510不僅具有高速的A/D轉(zhuǎn)換功能,而且還帶有內(nèi)部采樣保持電路,從而大大簡(jiǎn)化了外圍電路的設(shè)計(jì);同時(shí),由于其內(nèi)部帶有了標(biāo)準(zhǔn)分壓電阻,因而可以從+5V的電源獲得2V滿刻度的基準(zhǔn)電壓。TLC5510可應(yīng)用于數(shù)字TV、醫(yī)學(xué)圖像、視頻會(huì)議、高速數(shù)據(jù)轉(zhuǎn)換以及QAM解調(diào)器等方面。

2 內(nèi)部結(jié)構(gòu)、引腳說(shuō)明及工作原理

2.1 TLC5510的引腳說(shuō)明

TLC5510為24引腳、PSOP表貼封裝形式(NS)。其引腳排列如圖1所示。各引腳功能如下:

AGND:模擬信號(hào)地;

ANALOG IN:模擬信號(hào)輸入端;

CLK:時(shí)鐘輸入端;

DGND:數(shù)字信號(hào)地;

D1~D8:數(shù)據(jù)輸出端口。D1為數(shù)據(jù)最低位,D8為最高位;

OE:輸出使能端。當(dāng)OE為低時(shí),D1~D8 數(shù)據(jù)有效,當(dāng)OE為高時(shí),D1~D8為高阻抗;

VDDA:模擬電路工作電源;

VDDD:數(shù)字電路工作電源;

REFTS :內(nèi)部參考電壓引出端之一,當(dāng)使用內(nèi)部電壓分壓器產(chǎn)生額定的2V基準(zhǔn)電壓時(shí),此端短路至REFT端;

REFT:參考電壓引出端之二;

REFB:參考電壓引出端之三;

REFBS :內(nèi)部參考電壓引出端之四,當(dāng)使用內(nèi)部電壓基準(zhǔn)器產(chǎn)生額定的2V基準(zhǔn)電壓時(shí),此端短路至REFB端。

2.2 TLC5510的內(nèi)部結(jié)構(gòu)及工作過(guò)程

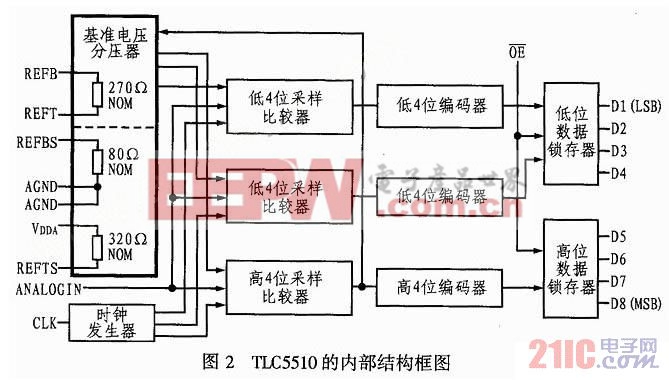

TLC5510的內(nèi)部結(jié)構(gòu)如圖2所示。由圖中可以看出:TLC5510模數(shù)轉(zhuǎn)換器內(nèi)含時(shí)鐘發(fā)生器、內(nèi)部基準(zhǔn)電壓分壓器、1套高4位采樣比較器、編碼器、鎖存器、2套低4位采樣比較器、編碼器和1個(gè)低4位鎖存器等電路。TLC5510的外部時(shí)鐘信號(hào)CLK通過(guò)其內(nèi)部的時(shí)鐘發(fā)生器可產(chǎn)生3路內(nèi)部時(shí)鐘,以驅(qū)動(dòng)3組采樣比較器。基準(zhǔn)電壓分壓器則可用來(lái)為這3組比較器提供基準(zhǔn)電壓。輸出A/D信號(hào)的高4位由高4位編碼器直接提供,而低4位的采樣數(shù)據(jù)則由兩個(gè)低4位的編碼器交替提供。

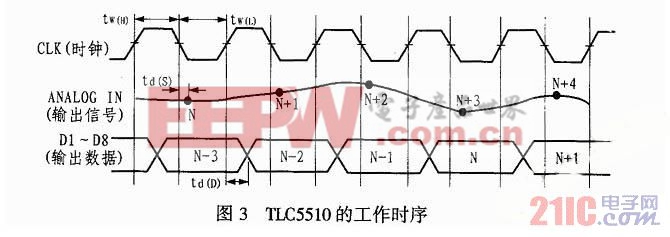

TLC5510的工作時(shí)序見(jiàn)圖3。時(shí)鐘信號(hào)CLK在每一個(gè)下降沿采集模擬輸入信號(hào)。第N次采集的數(shù)據(jù)經(jīng)過(guò)2.5個(gè)時(shí)鐘周期的延遲之后,將送到內(nèi)部數(shù)據(jù)總線上。

在圖3所示的工作時(shí)序的控制下,當(dāng)?shù)谝粋€(gè)時(shí)鐘周期的下降沿到來(lái)時(shí),模擬輸入電壓將被采樣到高比較器塊和低比較器塊,高比較器塊在第二個(gè)時(shí)鐘周期的上升沿最后確定高位數(shù)據(jù),同時(shí),低基準(zhǔn)電壓產(chǎn)生與高位數(shù)據(jù)相應(yīng)的電壓。低比較塊在第三個(gè)時(shí)鐘周期的上升沿的最后確定低位數(shù)據(jù)。高位數(shù)據(jù)和低位數(shù)據(jù)在第四個(gè)時(shí)鐘周期的上升沿進(jìn)行組合,這樣,第N次采集的數(shù)據(jù)經(jīng)過(guò)2.5個(gè)時(shí)鐘周期的延遲之后,便可送到內(nèi)部數(shù)據(jù)總線上。此時(shí)如果輸出使能OE有效,則數(shù)據(jù)便可被送至8位數(shù)據(jù)總線上。由于CLK的最大周期為50ns,因此,TLC5510數(shù)模轉(zhuǎn)換器的最小采樣速率可以達(dá)到20MSPS。

3 在線陣CCD數(shù)據(jù)系統(tǒng)中的應(yīng)用

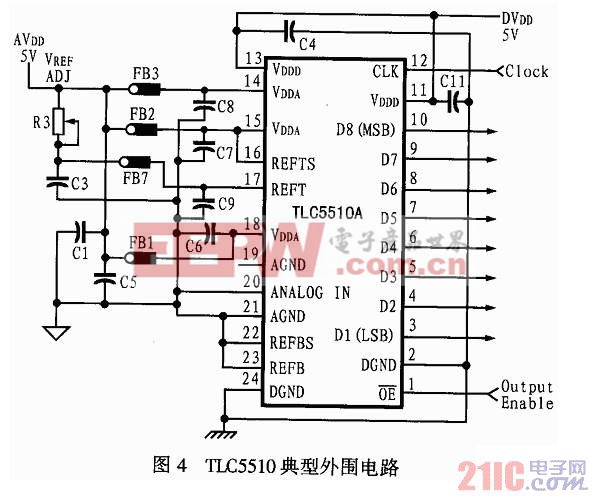

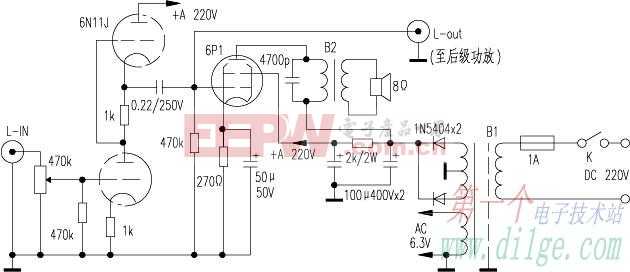

圖4 為T(mén)LC5510的典型外接電路。

圖中的FB1~FB3為高頻磁珠,模擬供電電源AVDD經(jīng)FB1~FB3為三部分模擬電路提供工作電流,以獲得更好的高頻去耦效果。

筆者研制的該線陣CCD數(shù)據(jù)采集系統(tǒng)主要由時(shí)序發(fā)生器、CCD驅(qū)動(dòng)電路、視頻信號(hào)預(yù)處理電路及ADC、數(shù)據(jù)存儲(chǔ)器、PC機(jī)等組成。TLC5510的高速、內(nèi)帶采樣保持電路等特點(diǎn)使其更利于該設(shè)計(jì)。TLC5510的主要作用是將CCD輸出的高速模擬視頻信號(hào)轉(zhuǎn)換為與其模擬幅值相對(duì)應(yīng)的8位數(shù)字視頻信號(hào)。圖5是筆者設(shè)計(jì)的視頻信號(hào)A/D轉(zhuǎn)換器TLC5510的外圍電路。TLC5510可使用外部和內(nèi)部?jī)煞N基準(zhǔn)電壓連接方法。其中外部基準(zhǔn)電壓從引腳REFT和REFB接入,并應(yīng)滿足:

VREFB+2V≤VREF≤VDDA

0≤VREFB≤VREFB-2V

2V≤VREFT-VREFB≤5V

對(duì)于從零電平開(kāi)始的正極性模擬輸入電壓,REFB應(yīng)當(dāng)連接到模擬地AGND。VREFT的范圍為2V~5V。如果要簡(jiǎn)化電路,可利用TLC5510的內(nèi)部分壓電阻從模擬電源電壓VDDA上取得基準(zhǔn)電壓。在本設(shè)計(jì)中,CCD輸出的模擬視頻信號(hào)經(jīng)過(guò)反相、濾波、放大之后即為從零電平開(kāi)始的正極性模擬電壓信號(hào)。因此,為了簡(jiǎn)化電路并同時(shí)滿足設(shè)計(jì)要求,筆者選用了TLC5510的內(nèi)部基準(zhǔn)方式,同時(shí),因?yàn)镃CD視頻信號(hào)是2V基準(zhǔn),所以,根據(jù)TLC5510的自身的特點(diǎn),在設(shè)計(jì)過(guò)程中,筆者將REFBS端與AGND,而將REFTS與VDDA端相連,同時(shí)將REFBS短接至REFB端,REFTS短接至REFT端來(lái)獲得2V基準(zhǔn)電壓。

在用該數(shù)據(jù)采集系統(tǒng)采集數(shù)據(jù)的過(guò)程中,當(dāng)CCD輸出端輸出視頻信號(hào)時(shí),在由時(shí)序發(fā)生器產(chǎn)生的A/D轉(zhuǎn)換控制時(shí)鐘CLK的同步控制下, TLC5510會(huì)將差動(dòng)放大、低通濾波后的CCD模擬視頻信號(hào)實(shí)時(shí)地轉(zhuǎn)換為與其模擬幅值相對(duì)應(yīng)的8位數(shù)字信號(hào),當(dāng)TLC5510的輸出使能 OE為低電平且高速數(shù)據(jù)存儲(chǔ)器的地址譯碼控制和寫(xiě)控制均有效時(shí),系統(tǒng)可將轉(zhuǎn)換結(jié)果存入高速數(shù)據(jù)存儲(chǔ)器,以等待PC機(jī)的讀取。為了使CCD輸出的視頻信號(hào)能夠正確可靠的轉(zhuǎn)換和存儲(chǔ),在設(shè)計(jì)過(guò)程中,筆者對(duì)TLC5510的工作控制時(shí)鐘CLK、輸出使能OE及高速數(shù)據(jù)存儲(chǔ)器的地址譯碼控制時(shí)鐘、讀寫(xiě)控制時(shí)鐘的周期做了具體的時(shí)間預(yù)算,并對(duì)它們之間的邏輯相位關(guān)系做了詳細(xì)的研究。根據(jù)預(yù)算,筆者將時(shí)序發(fā)生器內(nèi)部的計(jì)數(shù)器、比較器、邏輯門(mén)以及D觸發(fā)器等進(jìn)行逐級(jí)分頻和邏輯組合,從而使其產(chǎn)生正確可靠的時(shí)序邏輯。系統(tǒng)及數(shù)據(jù)分析實(shí)驗(yàn)證明,采用TLC5510作為線陣CCD視頻信號(hào)的A/D轉(zhuǎn)換芯片,其接口電路簡(jiǎn)單實(shí)用,使用方便,穩(wěn)定性好。

評(píng)論