在μC/OS―II上實現動態電壓調節技術

摘要 為了實現嵌入式實時操作系統對DVS的支持,本文在分析軟硬件兩方面節能原理的基礎上,提出了一個在實際應用中實現DVS的通用模型。該模型在μC/0S―II上得到了具體的實現。實現后的μC/OS―II被移植到支持離散頻率調整的開發板W90P710上。實驗結果表明,改進后的μC/OS―II節能效果顯著。

關鍵詞 電源管理 動態電壓調整 節能技術 低功耗 μC/OS―II

引 言

現代社會中,便攜式系統(如手機和個人媒體播放器)正在演變成綜合性多媒體和通信系統。新的應用程序,如游戲、數字電視、高速Internet,已經成為終端用戶產品中的一項普通功能。然而,復雜的功能需要功能強大的處理器,如智能手機中已集成了模擬基帶、數字基帶、圖像處理器和CPU等多個分處理器,但這些分處理器并不是任何時刻都是滿負載運轉的,它們在很多時候都處于閑置狀態。因此,對于依靠電池供電的便攜式設備,如何根據系統的工作狀態調整各個處理器的功耗水平從而節省電能便成了一個普遍關注的問題。

μC/OS―II作為一個源碼公開的嵌入式實時操作系統,可以支持64個任務,同時支持信號量、消息隊列、郵箱等多種常用的進程間通信方式。該操作系統用ANSI C語言書寫,程序可讀性強,移植性好,可裁減,并已在通信、電子、自動化等領域的嵌入式設備中獲得了廣泛的應用,但是它的內核并不支持DVS(Dynamic Voltage Scaling)管理。本文在遵循可移植、可裁減的前提下,對其進行了改進,使其可以支持動態的離散電壓管理,保證μC/OS―II在新要求下的應用,使嵌入式設備的電量能夠得到充分的使用。

1 DVS在μC/OS―II上應用的理論基礎

1.1 DVS應用的硬件基礎

動態電壓調節技術(DVS)是這樣一種技術:在保證系統任務完成的情況下,使處理器運行在盡可能低的電壓上。它的基本思想是,當系統需要完成大量計算任務時,提高處理器的電壓以增加其處理速度;而當系統任務較少或處于空閑狀態時,降低處理器的電壓,這樣既可以保證系統任務的按時完成,同時又可降低處理器的能量消耗。該節能技術的理論依據來自于對處理器功耗的定義:

![]()

其中:E為處理器的功耗,V為處理器的電壓,fclk為處理器的頻率,lLcak為漏電流;α和C為常數,分別表示門電路的電能轉換效率和門電路在整個設備中所占的比例;tTask表示系統中任務的個數。根據式(1)可知,通過降低處理器的電壓和頻率,可以減少處理器對電能的消耗。由于在實際應用中,程序能夠直接控制的是處理器的頻率,處理器的電壓會根據處理器頻率的變化自動變化。一般來說,處理器的電壓會隨著頻率的降低而降低,因此,動態電壓技術實際上是對頻率的調整。本文中如不作特別聲明,調整頻率即意味調整電壓。

1. 2 DVS應用的軟件基礎

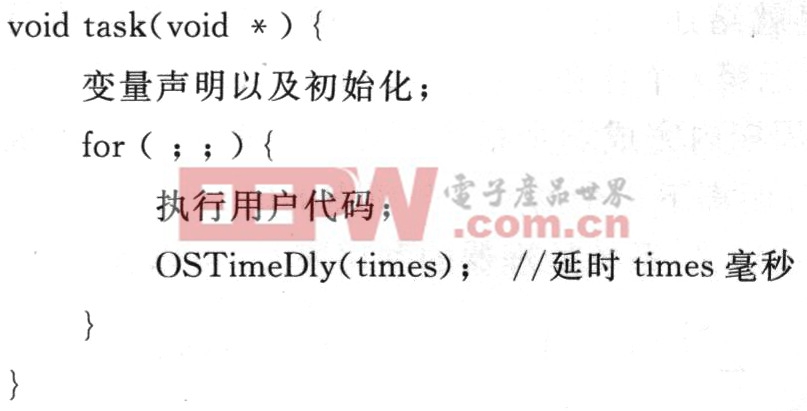

由于μC/OS―II是一個基于優先級的搶占式任務調度內核,為了保證低優先級任務能夠得到處理器的執行,本文假定系統中用戶定義的所有任務都遵循如下的結構:

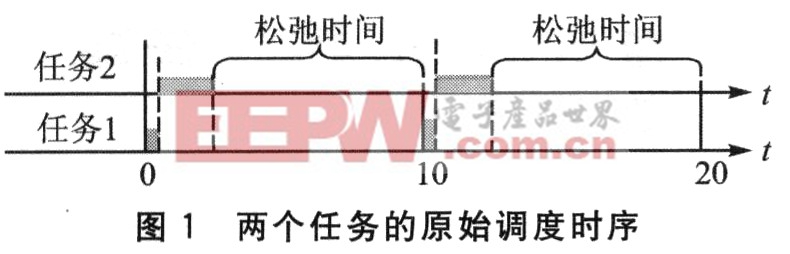

假設系統里有兩個任務:一個任務的執行時間為0.5 s,周期為10 s;另一個任務的執行時間為1 s,周期為5 s。這兩個任務的調度過程如圖l所示,這時系統中存在大量的松弛時間。

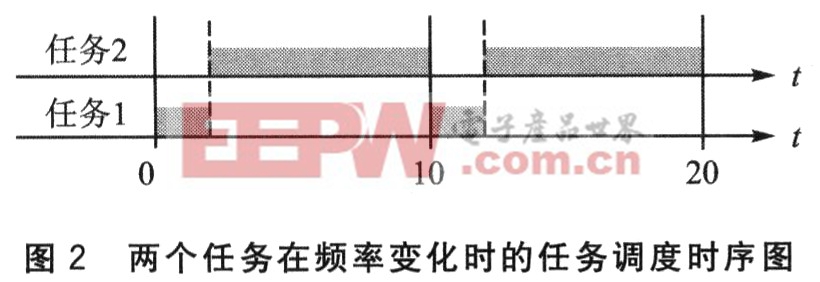

如果在程序運行過程中降低處理器的頻率,處理器的運行電壓也會因此變低。當處理器的頻率變化為最高頻率的1/4時,其任務調度過程如圖2所示。

由圖2可以知道,當處理器的頻率變化為正常的1/4時,系統任務仍然可以正常運行。這時,處理器的電壓下降了,根據式(1),處理器的功耗也降低了。

從上面的分析可以看出,正是由于μC/OS―II采用了基于優先級搶占的調度策略,每個任務執行一段時間之后,都會主動放棄CPU的使用,從而使低優先級的任務能夠得到執行。同時,由于任務放棄CPU進行延時操作,任務間會因此而產生松弛時間,而DVS功能就是利用這段松弛時問,降低處理器的執行速度而完成任務的。本文研究的重點就是改進μC/OS―II,使它能夠根據系統中任務運行產生的松弛時間的情況,自動設置處理器的頻率,降低電壓,從而降低處理器的功耗。

評論