簡易USB與LVDS接口轉換器

FPGA編程只需通過控制引腳,控制兩個并行信號的輸入輸出即可,同時可將數據的讀寫操作模塊化,從而進一步簡化系統編程。

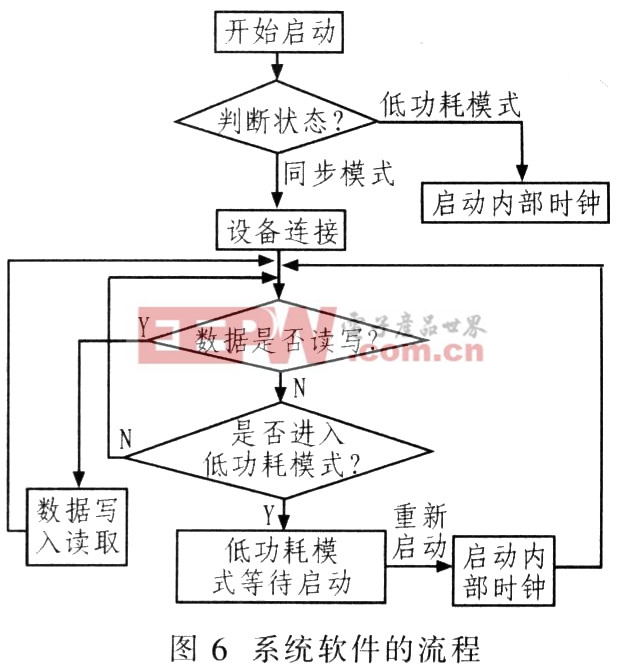

系統軟件設計流程如同6所示。由于遵循USB協議,在一段時間不進行任何操作時則進入低功耗模式。而USB3300也擁有這一特性。在一定時間系統不進行任何的讀寫操作,USB3300將進入低功耗模式,此時USB3300會自動關閉鎖相環時鐘輸出。本文引用地址:http://www.104case.com/article/181241.htm

所以在系統啟動后,首先判斷USB3300的狀態,如果在低功耗模式下,則控制STP信號開啟內部時鐘,進入到同步模式。

設備連接成功后,隨時判斷是否應該進行讀寫操作,若需要,則進入讀寫操作模塊,實現讀寫操作后又開始判斷讀寫。等待一段時間不執行讀寫操作后,USB3300則進入低功耗模式,關閉鎖相環,等待下次讀寫操作時再重新啟動內部時鐘。

5 結論

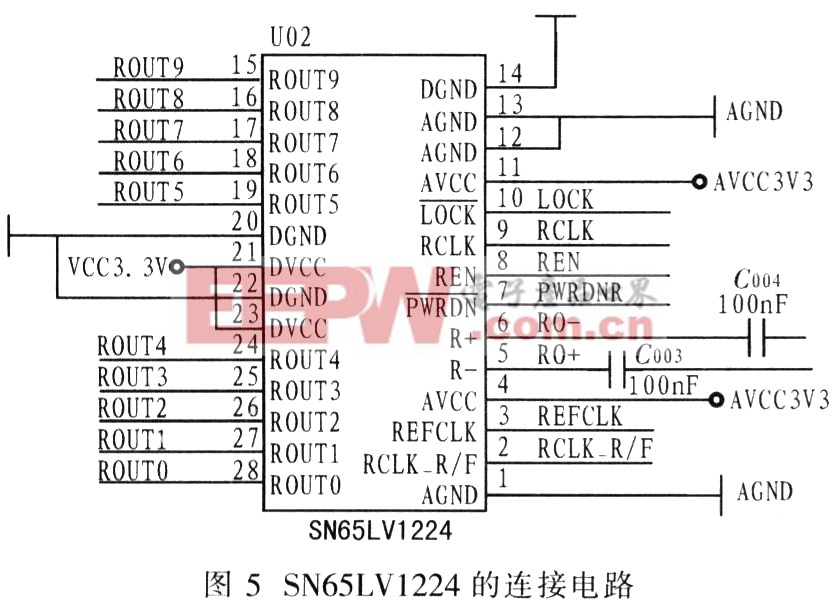

采用專用轉換器USB3300,SN65LV1023,SN65LV1224分別將USB協議物理層的差分信號和LVDS的低壓差分信號轉換成并行信號,并通過FPGA編程實現協議編程的轉換。該系統設計較為簡單,并且系統拓展較簡單,可易于實現USB接口、LVDS接口對多種接口的轉換。

由于串口通信協議的物理層信號較為復雜,FPGA直接與其物理層信號進行數據交互比較難以實現,難以做到時序同步,而采用專用的轉換器將串行信號轉換成并行數據信號,則大大簡化邏輯門陣列編程。該系統合理使用USB3300和SN65LV1023與SN65LV1224接口器件使得邏輯門陣列的編程易于實現,也可使用其他的專用轉換器,實現不同接口的轉換。

評論