簡易USB與LVDS接口轉換器

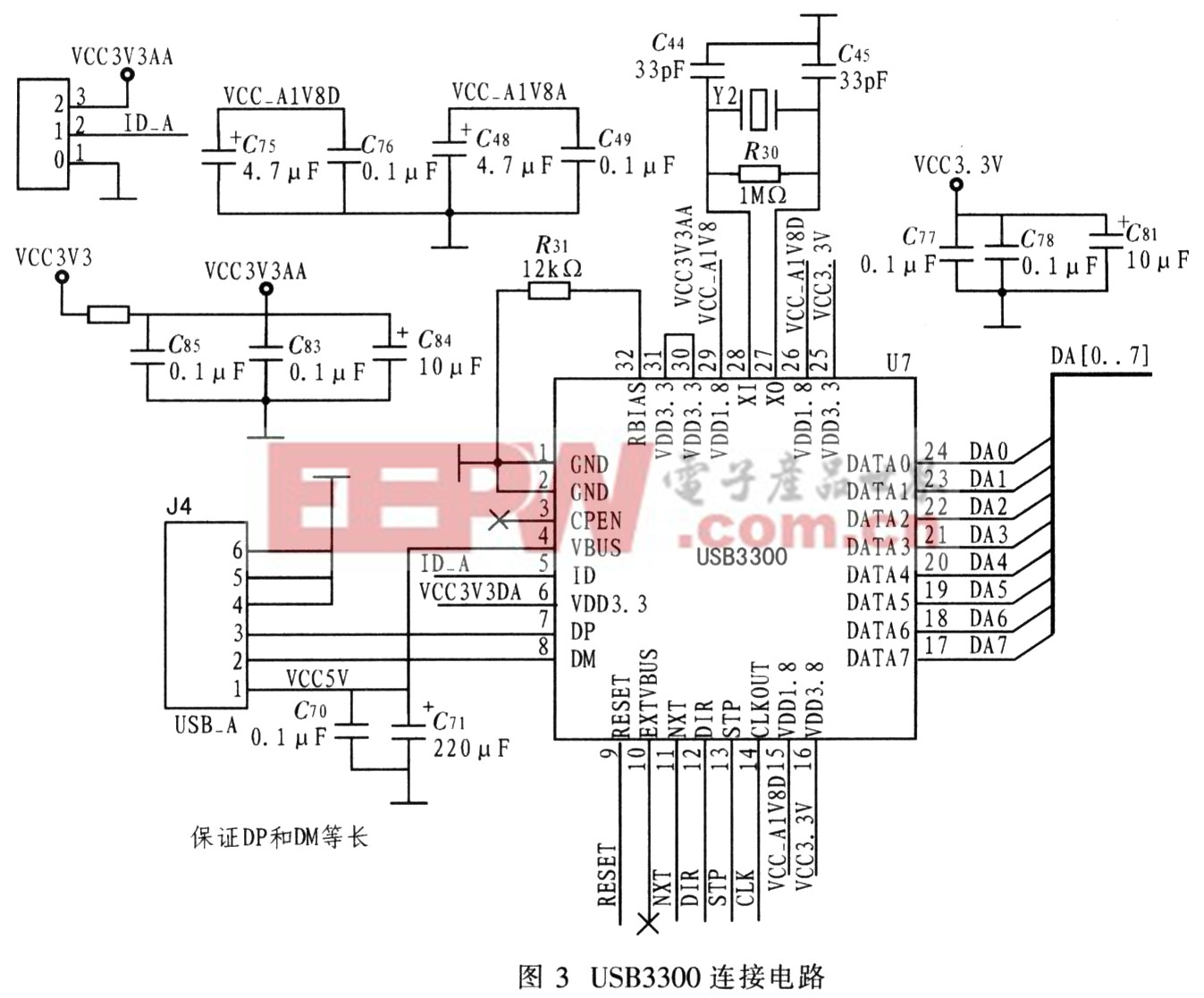

USB3300連接電路如圖3所示,為控制數據傳輸的時序同步,采用USB3300的時鐘輸出工作方式。USB3300外接24 MHz的時鐘晶體振蕩器,經內部鎖相環電路轉換為60 MHz信號,通過CLK輸入FPGA作為其時鐘信號,從而實現FPGA與USB3300的時鐘同步。USB接口部分與FPGA的數據交互傳輸通過雙向的8 位數據信號實現,USB3300通過DIR與NXT信號輸出控制數據信號的傳輸方向,而FPGA通過STP信號控制數據的傳輸方向USB3300的狀態。這樣便實現FPGA與USB3300的數據交互。本文引用地址:http://www.104case.com/article/181241.htm

3.3 協議數據轉換部分

系統協議數據轉換部分中采用現場可編程邏輯門陣列器件EP1C6U240C8進行編程,主要實現的功能是將與USB3300交互的數據轉換成10位并行數據與SN65LV1023和SN65LV1224交互,同時通過STP信號控制 USB3300的數據傳輸方向和USB3300的狀態。由于USB協議本身有低功耗模式,在低功耗模式時鎖相環關閉,在硬件設計時一定要接RESET控制鍵,這樣便于軟件編程的調試。

3.4 LVDS接口電路

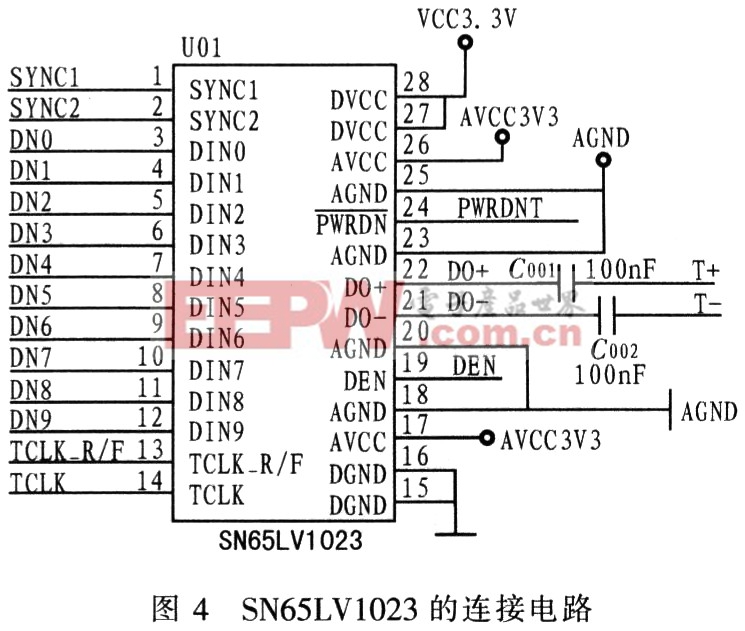

低壓差分信號LVDS(Low Voltage Differential Signaling)接口是一種高速數據傳輸的物理層接口,其電壓信號擺幅低,技術上能做到且產生極低噪聲,功耗也極低,主要用于服務器、可堆壘集線器、無線基站、3FG交換機及高分辨率顯示等。與USB協議接口類似其物理層信號直接與FPGA進行交互相當復雜,系統選用SN65LV1224和 SNLV1023,將FPGA與LVDS接口物理層數據交互,轉換為10位的并行信號,同時通過相關的控制信號控制數據的傳輸方向。SN65LV1023 與SN65LV1224的硬件連接電路分別如圖4和圖5所示,其中SN65LV1023實現10位并行數據轉換成LVDS的低壓差分信號,同時FPGA通過TCLK_R/F控制內部鎖相環,進而控制SN65LV1023狀態。而SN65LV1224則將LVDS的低壓差分信號轉換成10位并行數據信號輸入 FPGA,這樣通過SN65LV1023與SN65LV1224,便在較為簡單的情況下實現FPGA與LVDS接口的數據交互。

4 系統軟件設計

利用可編程邏輯門陣列FPGA轉換協議數據,由于系統使用USB3300可將USB協議物理層信號轉換成8位并行信號,而使用SN65LV 1023與SN65LV1224則將低壓差分信號LVDS轉換成10位并行信號,這樣大大簡化FPGA的編程。

評論