RocketIOTM GTP在串行高速接口中的位寬設(shè)計(jì)

對于這個(gè)問題,Xilinx提供了非對稱的異步FIFO,但這樣又會造成較大的延時(shí),同時(shí)無法避免圖4所示的DW組合轉(zhuǎn)換不當(dāng)?shù)膯栴}。這樣就使得FIF0的控制邏輯比較復(fù)雜,而數(shù)據(jù)的延時(shí)又較大,又會致使性能下降,有些得不償失,也不符合SATA2.0的高速低延遲要求。

為了降低延時(shí),同時(shí)簡化邏輯,筆者設(shè)計(jì)了一個(gè)滑動(dòng)窗口位寬轉(zhuǎn)換器,其中滑動(dòng)窗口的作用就在于尋找到正確的DW邊界,避免不當(dāng)?shù)腄W組合轉(zhuǎn)換。150 MHz時(shí)鐘和75 MHz時(shí)鐘的相位一致是這種轉(zhuǎn)換穩(wěn)定進(jìn)行的保障,而xilinx Virtex-5xc5vlx50t FPGA恰恰通過DCM提供了這樣兩個(gè)穩(wěn)定時(shí)鐘,因此,這兩個(gè)時(shí)鐘必須接到DCM響應(yīng)頻率的輸出。

利用3個(gè)18bit寄存器可以組成一個(gè)右移的寄存器組,輸入按[rxcharisk,rxdata]的形式組合成18 bit輸入數(shù)據(jù)。在位寬轉(zhuǎn)換開始后,通過判別中間寄存器的最高2 bit rxcharisk是否為2’bOl可判別DW的邊界,并選擇輸出數(shù)據(jù)來自哪個(gè)窗口。如果75 MHz時(shí)鐘有效沿檢測到中間寄存器最高2 bit rxcharisk是2’b01,則輸出reg2和regl重組后的36 bit數(shù)據(jù)。否則,就會輸出regl和reg0重組后的36 bit數(shù)據(jù)。但由于150 MHz時(shí)鐘和75 MHz時(shí)鐘存在著有效沿不一致的情況(即150 MHz時(shí)鐘的上升沿可能對應(yīng)著75 MHz時(shí)鐘的下降沿),75MHz時(shí)鐘有效沿可能會檢測到rxcharisk=2’b01,也可能永遠(yuǎn)檢測不到,這取決于復(fù)位之后初始輸入數(shù)據(jù)的特性。數(shù)據(jù)重組的作用是將2個(gè)相鄰的寄存器中的16bit數(shù)據(jù)(rxdata)及其2 bit類型指示(rxcharisk)信號重組為32 bit數(shù)據(jù)及其4 bit類型指示信號。DW邊界判別的依據(jù)是:在PHY連接建立之后,主機(jī)和設(shè)備之間會相互發(fā)送SYNC原語,表明兩端處于空閑狀態(tài),而SYNC就是一個(gè)控制(K)字節(jié),其低字接收后的xcharisk是2’bol,通過這個(gè)即可識別DW的邊界。

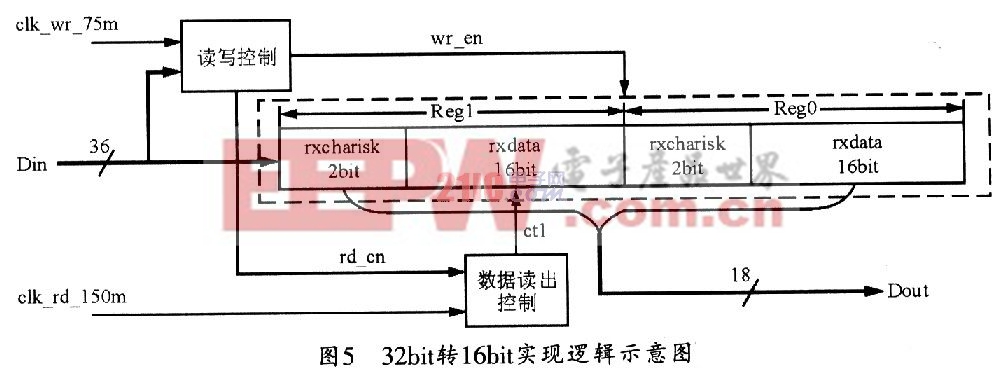

2.2 32 bit至16 bit位寬轉(zhuǎn)換模塊

根據(jù)上面16 bit至32 bit位寬轉(zhuǎn)換分析,需要將數(shù)據(jù)處理邏輯輸出的32 bit數(shù)據(jù)拆分成兩個(gè)16bit數(shù)據(jù)交給GTP進(jìn)行發(fā)送。同時(shí)在轉(zhuǎn)換的開始時(shí)刻,要求先發(fā)送一個(gè)DW的低字,然后發(fā)送其高字,而不能先發(fā)送一個(gè)DW的高字,否則接收端將無法正確恢復(fù)出DW。另外,150 MHz時(shí)鐘和75MHz時(shí)鐘的相位一致,同樣是這種轉(zhuǎn)換穩(wěn)定進(jìn)行的保障,因此,這兩個(gè)時(shí)鐘也必須接到DCM響應(yīng)頻率的輸出。其32 bit轉(zhuǎn)16 bit的實(shí)現(xiàn)邏輯示意圖如圖5所示。本文引用地址:http://www.104case.com/article/180728.htm

用2個(gè)18 bit的寄存器組寄存經(jīng)數(shù)據(jù)重組后的36 bit輸入數(shù)據(jù)時(shí),可根據(jù)輸入數(shù)據(jù)的控制字節(jié)(rxcharisk)指示位來判別數(shù)據(jù)的寫入和讀出。由于150 MHz時(shí)鐘和75 MHz時(shí)鐘存在著有效沿不一致的情況,即150 MHz時(shí)鐘的上升沿可能對應(yīng)著75 MHz時(shí)鐘的下降沿,因此,要準(zhǔn)確地進(jìn)行讀寫控制,就必須對wr_en和rd_en信號進(jìn)行同步。同步方法是利用75 MHz時(shí)鐘的有效沿(上升沿)與150 MHz時(shí)鐘有效沿一致的特性來同步產(chǎn)生wr-en和rd_en信號。而產(chǎn)生wr_en和rd_en信號的依據(jù)是在系統(tǒng)復(fù)位后,由數(shù)據(jù)處理邏輯向外發(fā)送SYNC信號來表明系統(tǒng)處于空閑(Idle)狀態(tài)。事實(shí)上,SYNC就是一個(gè)控制(K)字節(jié),其響應(yīng)的rxcharisk是4’b0001,通過這個(gè)可以正確地將DW寫入和讀出。DW的發(fā)送要求先發(fā)送低字,然后發(fā)送高字。數(shù)據(jù)讀出控制塊會利用rd-en信號使能2 bit的計(jì)數(shù)器,然后利用計(jì)數(shù)值將DW的低高字依次選擇讀出。

3 仿真及驗(yàn)證

通過對位寬轉(zhuǎn)換模塊的Verilog HDL描述,可在ModelSim se以及Xilinx ISE集成開發(fā)環(huán)境下進(jìn)行功能仿真和綜合布局布線后的時(shí)序仿真,也可在Xilinx Virtex-5 xc5vlx50t FPGA上進(jìn)行驗(yàn)證。圖6所示為16 bit轉(zhuǎn)32 bit邏輯仿真圖。而其32 bit轉(zhuǎn)16 bit邏輯仿真圖如圖7所示。

4 結(jié)束語

本設(shè)計(jì)可實(shí)現(xiàn)Virrex-5 RocketI0TM GTP進(jìn)行SATA2.0相關(guān)開發(fā)過程中的位寬匹配轉(zhuǎn)換功能,而且具有處理延遲小、差錯(cuò)率低等優(yōu)點(diǎn),并通過了Xilinx ISE綜合布線以及Virtex-5 FPGA上的驗(yàn)證,結(jié)果證明:本設(shè)計(jì)能夠完全滿足SATA2.0相關(guān)開發(fā)時(shí)序及功能上的要求。實(shí)際上,邏輯設(shè)計(jì)人員利用Virrex-5 RocketIOTM GTP進(jìn)行其他高速串行傳輸接口的開發(fā)時(shí),也可以借鑒此設(shè)計(jì)思想。

評論