RocketIOTM GTP在串行高速接口中的位寬設(shè)計(jì)

無論是在傳輸還是在操作過程中,都要保證每個(gè)Dword的正確性和完整性,否則將導(dǎo)致數(shù)據(jù)出錯(cuò)或原語流失。

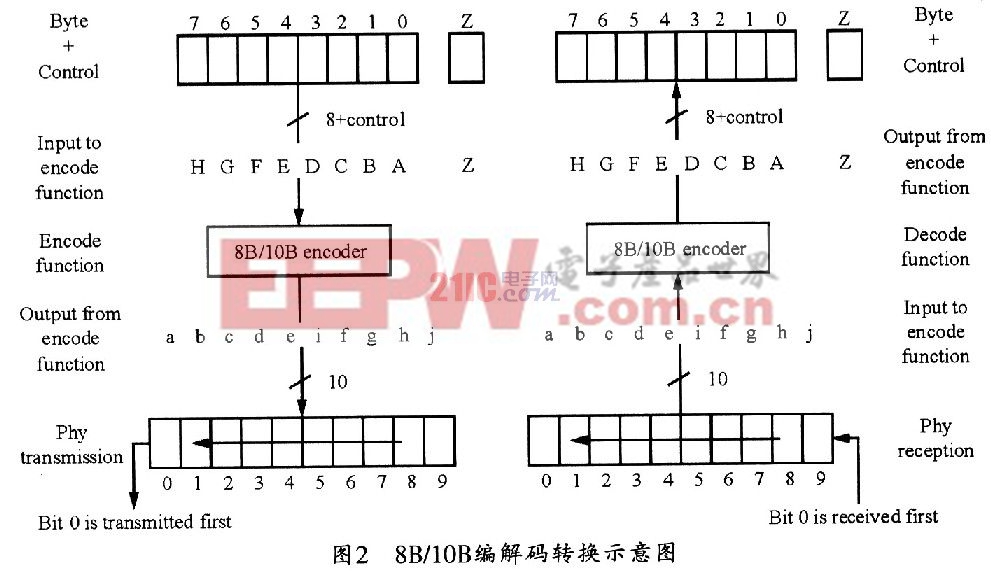

另外,目前高速數(shù)據(jù)傳輸接口或總線常用8B/10B編碼來編碼,其根本目的是實(shí)現(xiàn)直流平衡(DC Balance)。當(dāng)高速串行流的邏輯1或邏輯0有多個(gè)位沒有變化時(shí),信號(hào)的轉(zhuǎn)換就會(huì)因?yàn)殡妷何浑A的關(guān)系而造成信號(hào)錯(cuò)誤。直流平衡的最大好處便是可以克服以上問題。8B/10B編碼是目前許多高速串行總線采用的一種編碼機(jī)制,如1394b、Serial ATA、PCI Express、Infini-band、Fiber Channel、RapidIO等總線或網(wǎng)絡(luò),都是8B/10B編碼的擁護(hù)者。該編碼技術(shù)的基本精神很簡(jiǎn)單,就是將8個(gè)位經(jīng)過映射的機(jī)制轉(zhuǎn)化為10個(gè)位的字碼,但它平衡了位流中0與l的數(shù)量。

8B/10B編碼是將一組連續(xù)的8位數(shù)據(jù)分解成兩組數(shù)據(jù),一組3位,一組5位,經(jīng)過編碼后分別構(gòu)成一組4位代碼和一組6位代碼,從而組成一組10位的數(shù)據(jù)發(fā)送出去。相反,解碼是將l組10位的輸入數(shù)據(jù)經(jīng)過變換得到8位數(shù)據(jù)位。其8B/10B編解碼過程如圖2所示。本文引用地址:http://www.104case.com/article/180728.htm

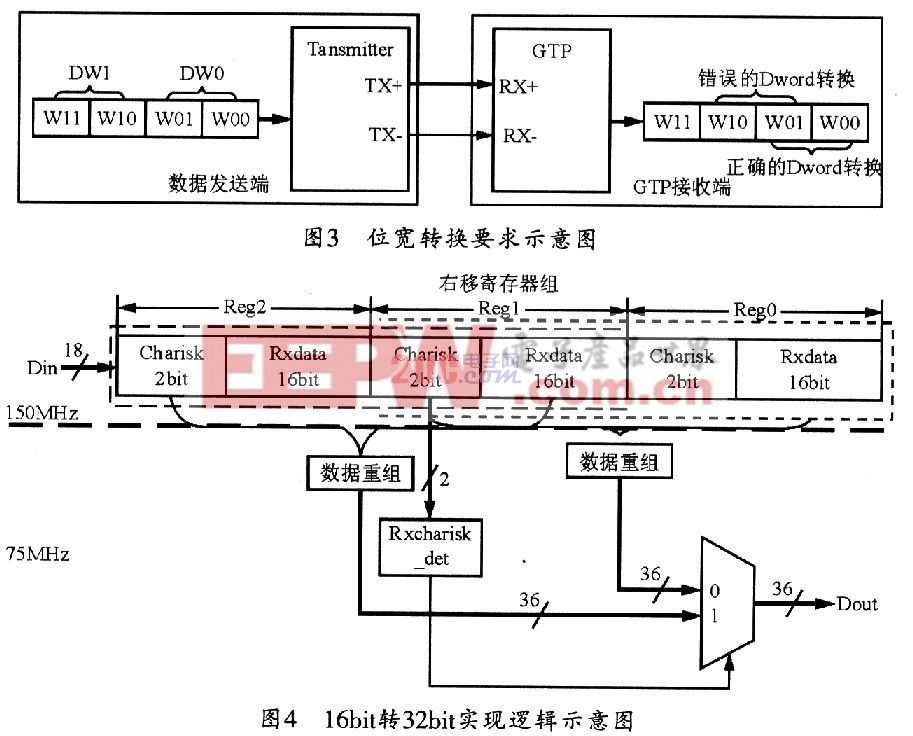

Xilinx公司推出的Virtex-5 FPGA以及配套的Virtex-5 RocketI0TM GTP收發(fā)器只支持16bit接口位寬的數(shù)據(jù)傳輸,即該GTP收發(fā)器是以word為數(shù)據(jù)處理單位。由于這與SATA2.0協(xié)議的相關(guān)規(guī)定出現(xiàn)了偏差,因而要求在數(shù)據(jù)進(jìn)入設(shè)計(jì)主體邏輯前后要進(jìn)行合并以及分解。同時(shí),F(xiàn)PGA中設(shè)計(jì)的數(shù)據(jù)處理邏輯是根據(jù)協(xié)議的要求而定義為75 MHz的時(shí)鐘域來進(jìn)行處理的,因此,在將數(shù)據(jù)交給FPGA中的數(shù)據(jù)處理主體邏輯之前,也必須進(jìn)行位寬的轉(zhuǎn)換。

由于GTP附帶的2 bit控制字節(jié)指示信號(hào)rxcharisk可用以表征接收到了K字符,故實(shí)際的數(shù)據(jù)需要從150 MHz (16+2) bit轉(zhuǎn)換為75 MHz(32+4)bit。但由于16 bit和32 bit的并行數(shù)據(jù)是主體。因此,筆者仍稱之為16 bit到32 bit位寬轉(zhuǎn)換和32bit到16 bit位寬轉(zhuǎn)換,它們實(shí)際上都包含了指示信號(hào),用來標(biāo)示該字符是否是控制字符。

2 位寬轉(zhuǎn)換

根據(jù)SATA2.0協(xié)議的規(guī)定和Virrex-5 RocketIOTM GTP的特性,以及SATA2.0接口邏輯中需要提取原語(primitive)進(jìn)行邏輯控制的要求,16bit和32 bit位寬的相互轉(zhuǎn)換不能簡(jiǎn)單的進(jìn)行word合并拆解,而是需要實(shí)現(xiàn)圖1中wordO和wordl的正確組合,否則將導(dǎo)致原語或數(shù)據(jù)受損,使控制邏輯無法獲得有效的交互原語,數(shù)據(jù)處理邏輯組幀傳輸錯(cuò)誤,文件損壞的狀況發(fā)生。這就要求系統(tǒng)能夠在提取原語和數(shù)據(jù)組幀之前,及時(shí)進(jìn)行Dword邊界校正,以保證后續(xù)處理的正確。

2.1 16bit至32bit位寬轉(zhuǎn)換模塊

該模塊將GTP接收后的150 MHz 16 bit并行數(shù)據(jù)轉(zhuǎn)換成數(shù)據(jù)處理邏輯可以工作的75 MHz 32 bit的并行數(shù)據(jù)。圖3所示為其位寬轉(zhuǎn)換要求示意圖。

由于在轉(zhuǎn)換開始時(shí),必須正確地將2個(gè)相關(guān)的16 bit Word組合成一個(gè)32bit DW,但不能將一個(gè)DW的低字跟相鄰的一個(gè)DW的高字組合成一個(gè)DW,否則邏輯處理時(shí)就會(huì)出錯(cuò)。圖4所示是16Bit轉(zhuǎn)32 bit的實(shí)現(xiàn)邏輯示意圖。

評(píng)論