Blackfin處理器低功耗設計

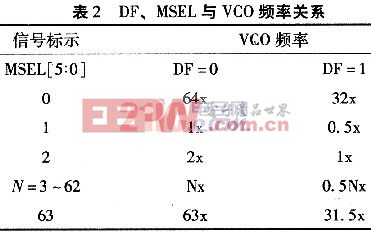

需要注意的是VCO最小輸出時鐘頻率為50 MHz,最大輸出頻率為內核時鐘CCLK頻率的最大值。對BlackfinBF533,CCLK最大值為600 MHz,而BF532/531的CCLK最大值為400 MHz。所以VCO輸出頻率不應超出范圍50MHz~CCLK。

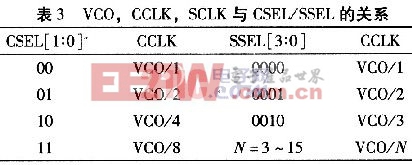

通過設置PLL分頻寄存器PLL_DIV中的CSEL(PLL_DIV的4~5位)確定CCLK,設置SSEL(PLL_DIV的0~3位)確定SCLK,具體對應關系如表3所示。

由于SCLK頻率不能高于CCLK的頻率,所以在對SSEL參數設置時,需要確定當前CCLK的頻率。

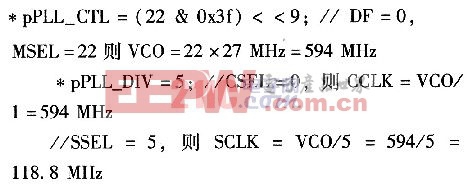

假設外部時鐘輸入CLKIN=27 MHz,將CCLK設置為594 MHz(27×22),SCLK設置為118.8 MHz(594/5),程序代碼如下

評論