Blackfin處理器低功耗設計

摘要:Blackfin處理器廣泛應用于便攜音視頻產品等嵌入式系統,低功耗設計直接影響產品使用時間。文中從時鐘頻率、工作模式、片內外設、內核電壓等方面,說明了Blackfin處理器低功耗設計的具體方法,根據實際應用實現對系統功耗的靈活控制與調節,最大程度上延長系統的有效使用時間。

關鍵詞:DSP;Blackfin;低功耗

Blackfin處理器功耗由內部功耗、外部功耗和實時鐘功耗組成。內部功耗由內部動態電流和靜態電流引起。外部功耗取決于處理器內外設的使用情況,在不同的應用場合,片內外設的使用有所不同,外部功耗也會不同。實時鐘功耗一般處于特定范圍之內,工作溫度為25~85℃時,實時鐘功耗范圍為0.067~0.1825mW。Blackfin系列處理器提供了動態電源管理功能,靈活的對時鐘頻率、工作模式及內核電壓進

行調整,以Blackfin533為例闡述Blackfin系列處理器低功耗設計的具體方法。

1 時鐘頻率控制

現代DSP芯片中大量使用CMOS FET(Complementary Metal-oxide Semiconductor FET互補金屬氧化物場效應管)開關,穩定時或者處于完全打開狀態(很低的負載),或者處于完全關閉狀態,但是在兩種狀態轉換過程中會產生漏電流,所以開關頻率很高時,FET充放電會引起很大的電源功耗。因此,通過降低系統時鐘頻率可以有效降低系統功耗。

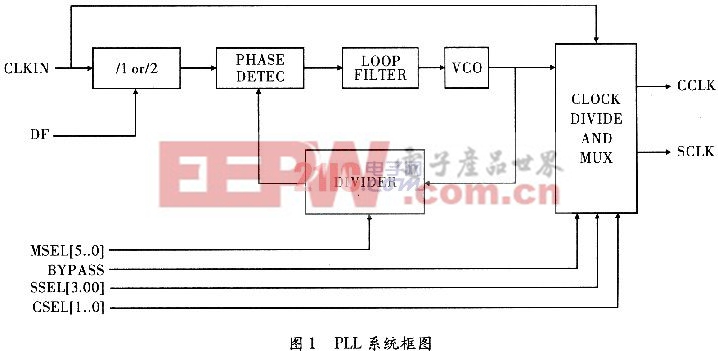

Blackfin533通過外部時鐘輸入引腳CLKIN接收外部時鐘源(10~40 MHz)的時鐘輸入,再通過鎖相環(PLL),電路模塊產生內核時鐘(CCLK)和系統時鐘(SCLK),通過設置PLL相關寄存器實現對CCLK和SCLK的頻率控制。PLL系統如圖l所示。

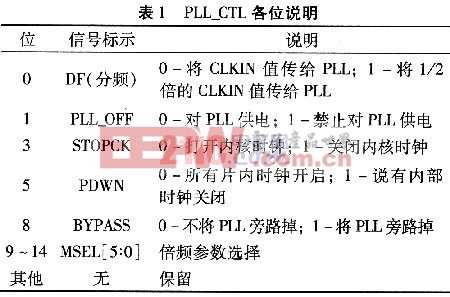

CCLK和SCLK均由VCO(Voltage-ControlledOscillator-壓控振蕩器)輸出的時鐘分頻后得到。VCO輸出時鐘頻率由PLL控制寄存器(PLL_CTL)設置,CCLK和SCLK對VCO的分頻因子由PLL分頻寄存器(PLL_DIV)設置。PLL_CTL各位說明如表1所示。

對于不同的DF和MSEL值,VCO輸出相應的時鐘頻率,對應關系如表2所示。

評論