一種高精度BiCMOS電流模帶隙基準源

2 帶隙基準電路仿真結果

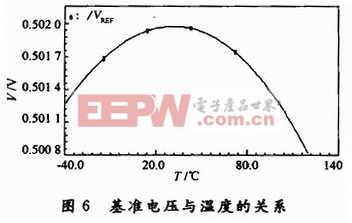

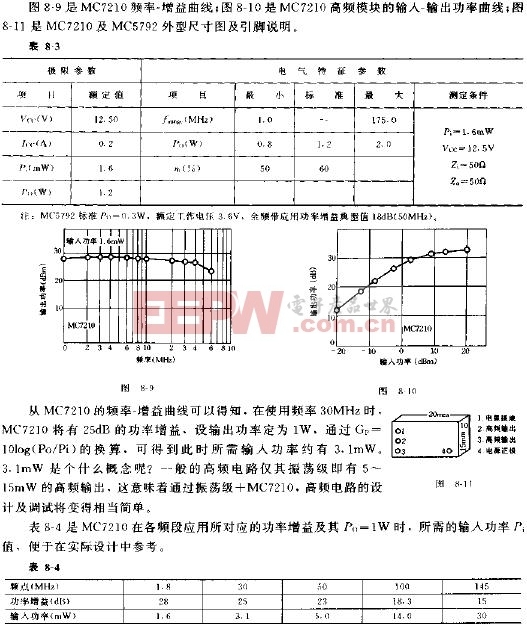

電路采用Xfab O.35μm BiCMOS的工藝模型庫,用Cadence Specte仿真器對電路進行仿真模擬。當電源電壓為3.3 V時,圖6和圖7分別是溫度相關性和電源抑制比(PSRR)的曲線圖。結果顯示,本帶隙基準輸出O.5 V穩定電壓,在-40~+125℃的溫度范圍內,溫漂為15 ppm,電路表現出良好的溫度特性。同時,低頻時基準電壓源的電源抑制比可達-103 dB,在40 kHz以前電源抑制比小于-100 dB。圖8是本電路在不同工作電壓下的輸出電壓,可見電路正常啟動電壓為2 V,電路啟動后基準電壓的變化小于O.06 mV。

3 結語

帶隙基準電壓電路作為模擬電路中的重要模塊對A/D采集精度、電源管理芯片的性能都有重要影響。本文設計了一種高精度、高電源抑制比、低電壓的帶隙基準電路,并且實現了對基準電壓的外部修調。結果表明:電路在3.3 V電源電壓,-40~+125℃下能提供穩定的0.5 V基準電壓輸出,溫漂15 ppm,低頻時電源抑制比-103 dB,達到了設計要求。

評論