基于反相SEPIC的高效率降壓/升壓轉換器的實現

ADP1877具有脈沖跳躍模式,使能時,可以降低開關速率,只向輸出端提供足以保持輸出電壓穩定的能量,從而提高小負載時的效率,大大降低柵極電荷和開關損耗。在同步反相SEPIC和同步降壓拓撲結構中均可以使能此模式。圖4所示DC-DC轉換電路只需要雙通道ADP1877的一個通道,因此另一通道可以用于任一種拓撲結構。

電感耦合和能量傳輸電容

圖4中,功率電感L1A和L1B顯示為彼此耦合。在這種拓撲結構中,耦合電感的目的是減少輸出電壓和電感電流的紋波,并且提高最大可能閉環帶寬,下一部分將對此加以說明。

雖然這些電感互相耦合,但并不希望耦合太緊,以至于將一個繞組的大量能量通過鐵芯傳輸至另一個繞組。為了避免這一點,必須求得耦合電感的泄漏電感(LLKG),并選擇適當的能量傳輸電容(CBLK2),使得其復數阻抗的幅值為泄漏電感與單個繞組電阻(DCR)的復串聯阻抗的1/10,如方程式2、3、4所示。按照這一關系設計電路,可使耦合鐵芯所傳輸的能量降至最低。泄漏電感可以根據耦合電感數據手冊中提供的耦合系數計算。

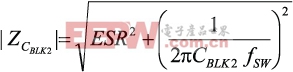

| (2) |

| (3) |

| (4) |

匝數比最好為1:1,因為對于給定水平的輸出電壓紋波,此時各繞組只需要分立電感所需電感的一半1。可以使用1:1以外的匝數比,但其結果將無法用本文中的方程式準確描述。

小信號分析和環路補償

反相SEPIC轉換器的完整小信號分析超出了本文的范圍,不過,如果遵照下述原則,完整分析將更具學術意義。

首先必須計算諧振頻率(fRES)時的許多復數阻抗交互,以便求得目標交越頻率的上限。當電感解耦時,此頻率降低,導致最大可能閉環帶寬顯著降低。

| (5) |

在此頻率時,可能有300°或更大的“高Q”相位遲滯。為了避免轉換器在整個負載范圍內相位裕量偏小的問題,目標交越頻率(fUNITY)應為fRES的1/10。此諧振的阻尼主要取決于輸出負載電阻和耦合電感的直流電阻。在較小程度上,阻尼還取決于能量傳輸電容的等效串聯電阻(ESR)和功率MOSFET(QHl和QL1)的導通電阻。因此,當輸出負載電阻改變時,閉環傳遞函數的特征在該頻率時發生明顯變化也不足為奇。

耦合系數通常不是一個能夠精確控制的參數,因此應將目標交越頻率設置為比fRES低10倍的值(假設fRES小于開關頻率fSW)。當fUNITY設置適當時,可以使用標準“II型”補償——兩個極點和一個零點。

| (6) |

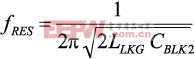

圖6顯示同步反相SEPIC降壓/升壓拓撲結構中ADP1877反饋環路的等效電路。上框包含功率級和電流環路,下框包含電壓反饋環路和補償電路。

圖6. 同步反相SEPIC拓撲結構中ADP1877具有內部電流檢測I環路的功率級和補償方案

評論