一種基于CPLD的QDPSK調制解調電路設計

2.3 利用CPLD設計的QDPSK調制解調電路

將設計的QDPSK調制電路“qdpskb”組件和解調電路“qdpsky”組件連接在一起,為了仿真實驗方便,信碼數據輸入采用四級偽隨機碼電路——從MAX+PLUSⅡ器件庫中調用4個D觸發器、2個異或門和1個四或非門,解調電路中位定時恢復電路產生的數據時鐘直接采用qdpsk調制電路數據時鐘,調制解調電路直接相連,組成的QDPSK調制解調電路如圖5所示。本文引用地址:http://www.104case.com/article/179912.htm

QDPSK調制解調電路的引腳關系為:引腳clk表示數據時鐘輸入,引腳k1表示數據時鐘clk的八分頻輸出,引腳data表示四級偽隨機碼電路數據輸出,引腳c0、c1、c2、c3表示四相載波。引腳p1和p2表示信碼數據data在時鐘的作用下串并轉換后的輸出,引腳cx和cy表示差分編碼后的輸出,引腳qdpsk表示四相差分移相鍵控信號輸出。引腳qx和qy表示四相差分移相鍵控信號的相干解調輸出,引腳x和y表示差分譯碼后的輸出,引腳out表示信碼差分譯碼后經并串轉換恢復的信碼數據輸出。

3 實驗結果

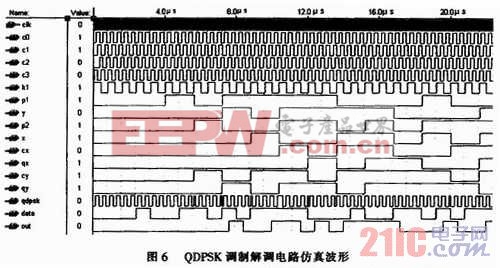

利用MAX+PLUSⅡ開發工具建立波形輸入文件,在File菜單里面選擇New打開新建文件類型對話框,選擇Waveform Editor File項,單擊“OK”。在波形編輯器窗口的Name下單擊鼠標右鍵,出現浮動的菜單,選擇Enter Nodesfrom SNF…可以打開“從SNF文件輸入觀測點”的對話框。在Type區選擇Input和Output,在默認的情況下是打開的,單擊“List”按鈕,可在Available Nodes&Groups區看到設計文件中使用的輸入/輸出信號,單擊“=>”按鈕可以將這些信號選擇到Selected N0des&Groups區。單擊“OK”按鈕,關閉對話框即可看到波形編輯窗口,將此波形文件保存為默認名。在波形文件中添加輸入/輸出信號名后,就可以開始對輸入信號建立波形了。QDPSK調制解調電路仿真波形如圖6所示。

圖6中“clk”表示輸入時鐘,“c0”、“c1”、“c2”、“c3”表示四相載波.“k1”表示數據時鐘clk的八分頻輸出,“data”表示

四級偽隨機碼電路數據輸出,“p1”、“p2”表示信碼數據data串并轉換后的輸出,“cx”、“cy”表示信碼數據串并轉換后差分編碼的輸出,“qdpsk”表示輸入的信碼數據四相差分移相鍵控信號輸出。“qx”、“qy”表示四相差分移相鍵控信號的相干解調輸出,“x”、“y”表示相干解調輸出后差分譯碼輸出,“out”表示信碼差分譯碼后經并串轉換恢復的信碼數據輸出。

仿真結果表明:QDPSK調制電路能正確選相,解調電路輸出數據在延時約5.2μs后,與QDPSK調制輸入數據完全一致。

將綜合后生成的網表文件通過ByteBlaste下載電纜,以在線配置的方式下載到CPLD器件EPM7128SLC84-15中,從而完成了器件的編程。上電后,在輸入端加入數據時鐘,用數字存儲示波器測試調制解調電路輸出,實測結果完全正確,表明達到了設計要求。

4 結論

本文利用CPLD器件,設計出的QDPSK調制解調電路,利用了EDA技術中的MAX+PLUSⅡ作為開發工具,將設計的電路圖綜合成網表文件寫入其中,制成ASIC芯片。其突出優點是自頂向下設計,查找和修改錯誤方便,同時先仿真,正確后再下載測試并應用,具有較大的靈活性;調制和解調放在一塊芯片上,集成度非常高;解調電路輸出數據延時約5.2μs,數據速率快。本文提出的QDPSK調制解調電路,已應用于小型數據傳輸系統中。

評論