一種基于CPLD的QDPSK調制解調電路設計

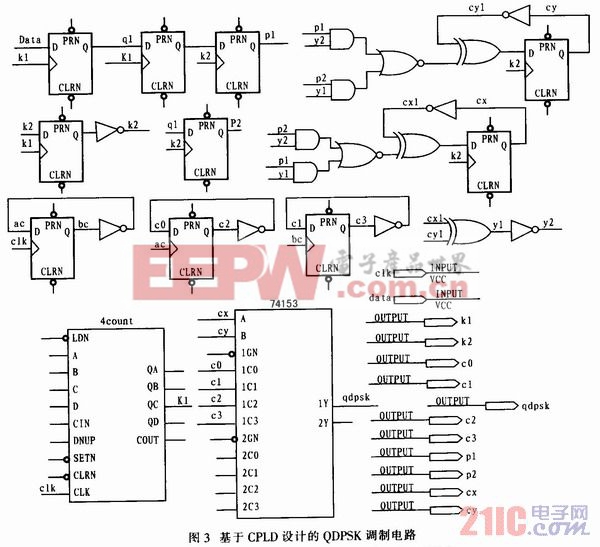

圖3所示QDPSK調制電路引腳關系為:引腳k1表示數據時鐘clk經過計數器4count的八分頻輸出,引腳k2表示數據時鐘k1的二分頻輸出,引腳ac和bc表示數據時鐘clk的二分頻輸出和二分頻反相輸出,引腳c0和c2表示數據時鐘ac的二分頻輸出和二分頻反相輸出,引腳c1和c3表示數據時鐘bc的二分頻輸出和二分頻反相輸出,c0、c1、c2和c3組成四相載波。引腳p1和p2表示輸入信碼數據data在時鐘的作用下串并轉換后的輸出。引腳cx和cy表示信碼數據串并轉換后,在同步時鐘的作用下差分編碼后的輸出,引腳qdpsk表示輸入的信碼數據在同步時鐘的作用下四相差分移相鍵控信號輸出。

圖3所示電路器件均可從MAX+PLUSⅡ器件庫中調用。其中二分頻電路涮用1個D觸發器和1個非門組成;串并轉換電路調用4個D觸發器組成;差分編碼電路調用2個二異或門、2個D觸發器、4個2與門、2個或非門和2個非門組成:四相選相電路調用1個74153組成。調制電路在MAX+PLUSⅡ平臺上編譯、仿真通過后,打包產生qdpskb組件。

2.2 QDPSK解調電路

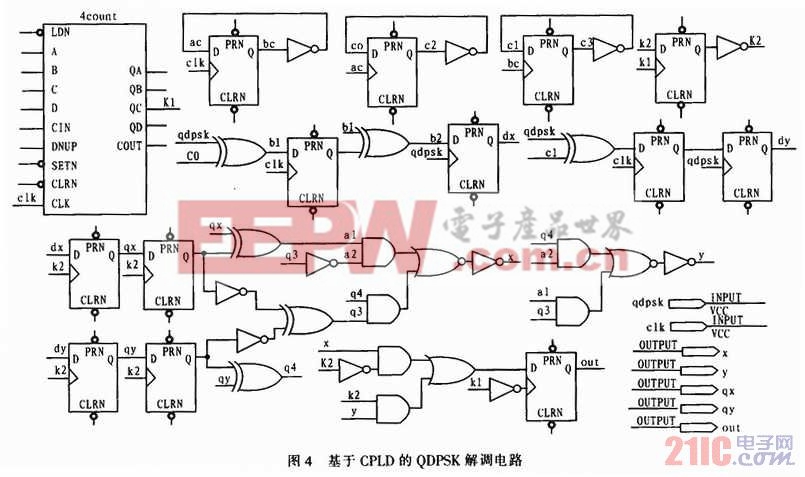

基于CPLD設計的QDPSK解調電路如圖4所示。

圖4所示QDPSK解調電路引腳關系為:引腳clk表示恢復的數據時鐘,引腳k1表示數據時鐘clk經過計數器4count的八分頻輸出,引腳k2表示數據時鐘k1的二分頻輸出,引腳ac和bc表示數據時鐘clk的二分頻輸出和二分頻反相輸出,引腳c0和c2表示數據時鐘ac的二分頻輸出和二分頻反相輸出,引腳c1和c3表示數據時鐘bc的二分頻輸出和二分頻反相輸出,c0、c1、c2和c3組成四相載波。引腳qdpsk表示四相差分移相鍵控信號輸入,引腳qx和qy表示四相差分移相鍵控信號的相干解調輸出。引腳x和y表示相干解調輸出在同步時鐘的作用下差分譯碼后的輸出,引腳out表示信碼差分譯碼后經并串轉換恢復的信碼數據輸出。

電路器件從MAX+PLUSⅡ器件庫中調用。其中二分頻電路調用1個D觸發器和1個非門組成;相干解調電路調用3個異或門、6個D觸發器組成;差分譯碼電路調用2個D觸發器、3個異或門、5個非門、4個與門和2個或非門組成;并串轉換電路調用2個非門、2個與門、1個或門和1個D觸發器組成。解調電路在MAX+PLUSⅡ平臺上編譯、仿真通過后,打包產生qdpsky組件。

評論