基于EL7558BC的DC/DC變換器的設計與實現

ΔIL為允許的最大輸出電感紋波電流值,這個值通常必須小于0.8A。

電容的選擇要從電容直流額定電壓,電容的額定紋波電流,電源的最大輸出紋波電壓,電源的穩定性等四個因素去考慮。電容額定電壓必須大于輸出電壓,一般至少要比輸出電壓高出10%,以控制紋波和瞬態響應。最大的電容紋波電流(即電容RMS電流)可以用式(6)計算,所選電容的額定紋波電流必須大于式(6)的計算結果。

IC(RMS,MAX)=![]() (6)

(6)

式中:IC(RMS,MAX)為最大的電容RMS電流。

對于電源的最大輸出紋波電壓,首先,要確定具體應用對輸出紋波電壓的要求,EL7558BC芯片輸出紋波電壓必須限制在輸出電壓的2%以內。接著,利用式(7)計算允許的電容最大ESR,選擇最大額定ESR小于式(7)計算值,以確保輸出紋波電壓符合應用要求。另外,電容ESR的溫漂也必須考慮在內。

ESRMAX′=![]() (7)

(7)

式中:ESRMAX為允許的最大輸出電容ESR;

ΔV(MAX)為允許的最大輸出紋波電壓值;

ΔIL(MAX)為允許的最大輸出紋波電流值,這個值通常必須小于0.8A。

可以通過多個電容并聯的方法來降低ESR,提高電路的瞬態響應,不過總的ESR必須大于10mΩ,總的電容值必須大于330μF。

2.5 布局布線注意事項

在布局布線時,原則是所有的外圍元器件要盡可能的靠近EL7558BC電源芯片,尤其是去耦電容和旁路電容必須布在相應的管腳附近。EL7558BC器件有兩個地(模擬地和電源地),模擬地連接所有噪聲敏感信號,而電源地連接有噪聲的信號。兩個地之間引入噪聲將降低芯片的性能,尤其在大電流輸出的情況下。但是,模擬地的噪聲過大將會影響控制信號,所以,推薦把模擬地和電源地分開,并且兩個地在一點(通常在芯片下面或者在輸入或輸出電容的負邊)直接連接以降低兩個地之間的噪聲。連接反饋腳(腳1和腳28)的走線對噪聲最為敏感,要盡可能地短,最好布在兩個地線中間。

EL7558BC芯片的散熱主要靠VSSP引腳以及芯片底部的散熱焊盤。為了達到良好的散熱性能,散熱焊盤必須完全焊接在PCB上,如果有中間的地層時,必須通過多個過孔把地層與散熱焊盤相連以提高散熱效果。

3 結語

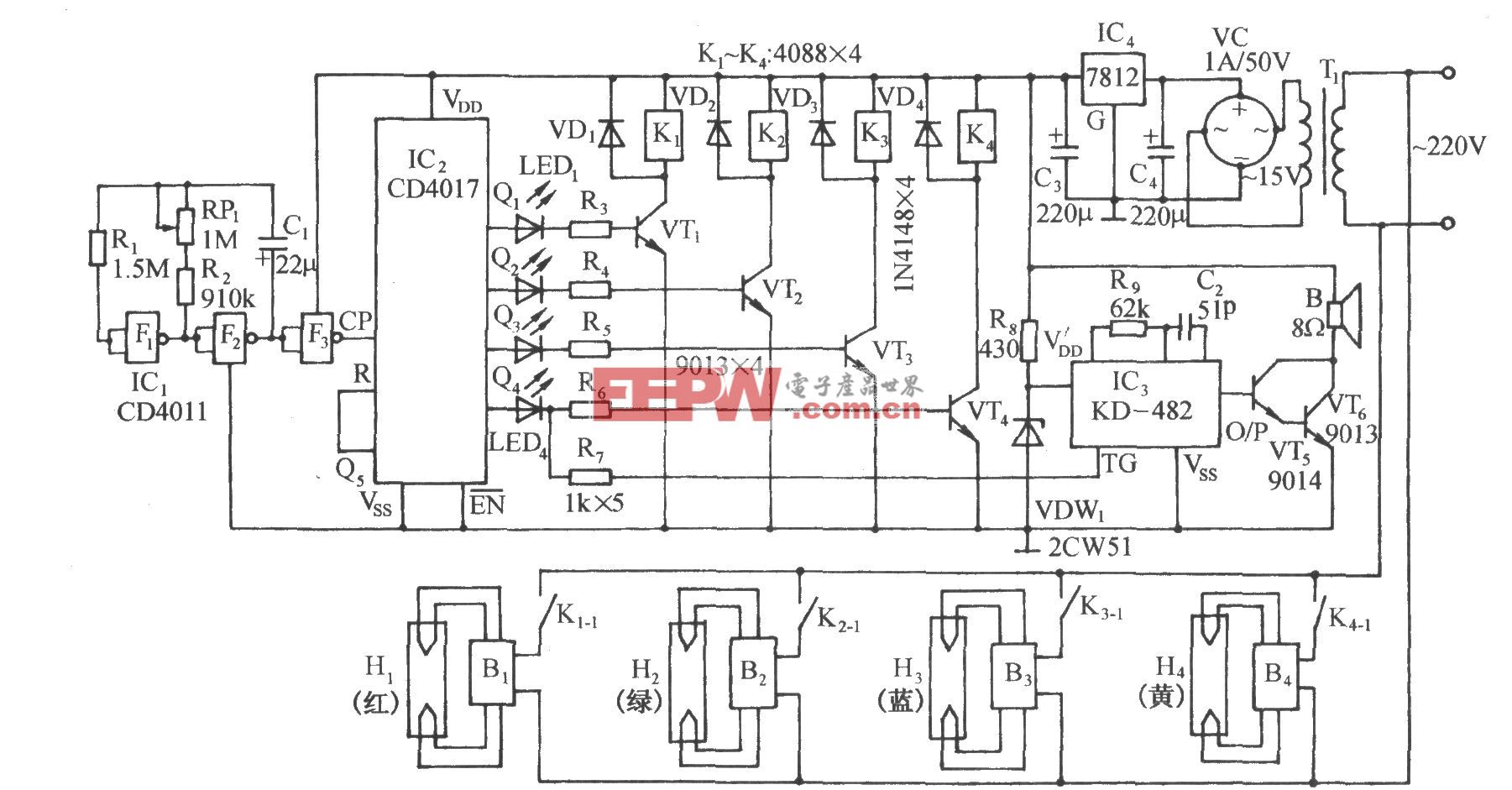

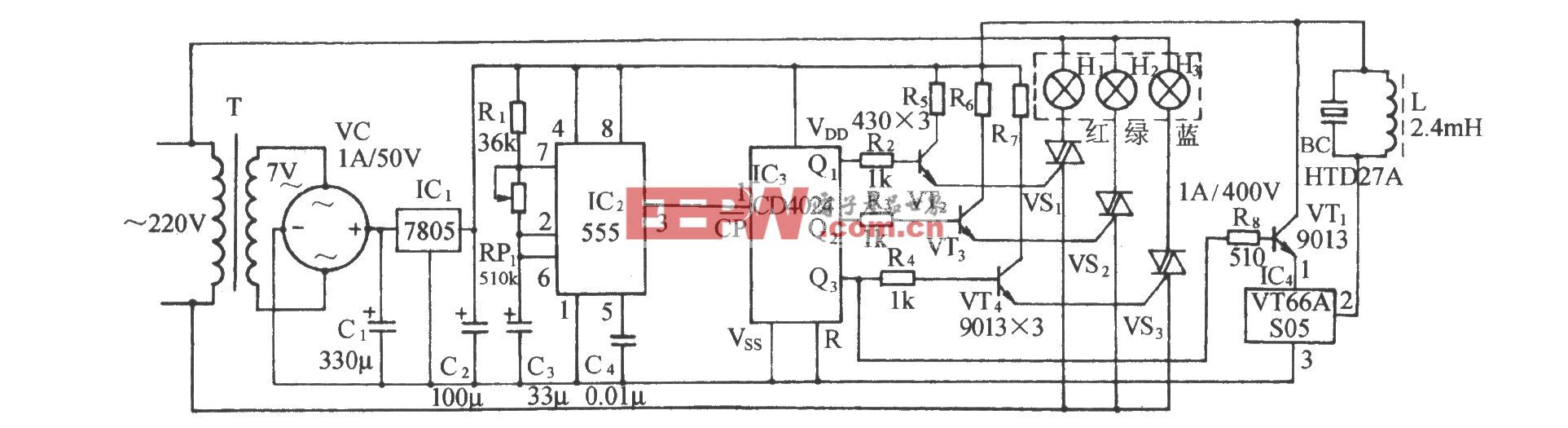

我們采用以上方法,用兩塊EL7558BC芯片設計了基于FPGA的MPEG4解碼器芯片設計演示開發板的電源(輸入4.5~5.5V,輸出3.3~1.5V)。其中3.3V輸出的設計電路如圖1所示,各項指標如下:

1)輸出電壓校準在輸入電壓從4.5V到5.5V及負載電流從0到8.0A的范圍內變化時,輸出電壓變化不超過1.0%;

2)負載瞬態響應負載電流在15μs內從0A到8A或從8A到0A突變,輸出電壓瞬時波動不超過120mV,波動時間不超過25μs;

3)輸出電壓紋波在輸入電壓為4.5~5.5V時,輸出電壓紋波峰峰值低于22mV。

4)輸入電壓紋波在負載為8A,輸入電壓為4.5~5.5V時,輸入電壓紋波峰峰值大約為230mV,增大輸入電容值,將C9從220μF換成470μF,輸入電壓紋波峰峰值降到180mV左右。

基于EL7558BC的 DC/DC模塊設計體現了新型的快速,簡易的電源解決方案,其設計方法在目前的DC/DC變換器設計中是非常典型的,具有相當的參考價值。

評論