一種低功耗64 倍降采樣多級數字抽取濾波器設計

5 仿真與驗證

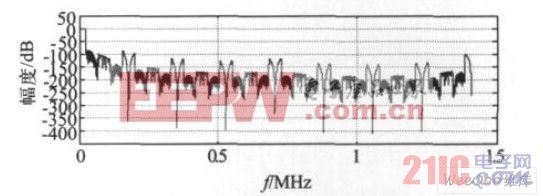

在matlab 下對64 倍降采樣及連抽取濾波器的幅頻響應進行仿真,結果如圖10 所示,其中補償濾波器和半帶濾波器的系數經過了截位處理。

圖10 系統總幅頻特性曲線

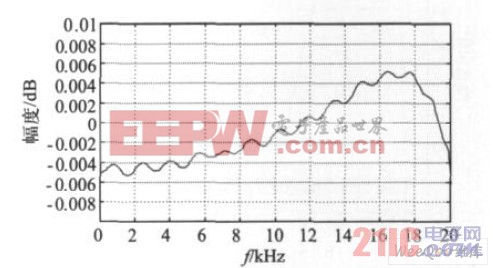

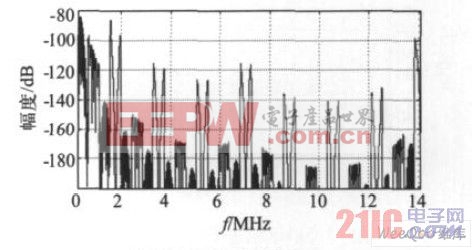

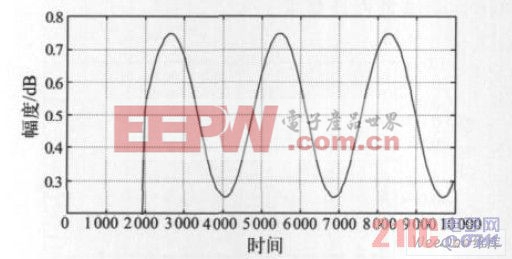

對數字濾波器的通帶紋波與阻帶衰減特性進行仿真,相應的幅頻響應曲線如圖11和圖12所示。系統總通帶紋波為± 0.006dB,阻帶衰減在80dB以下,總體性能滿足設計要求。

圖11 系統通帶特性

圖12 系統阻帶特性

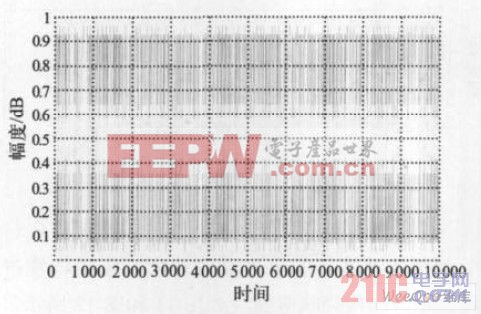

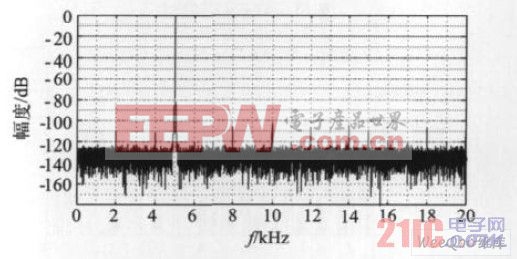

在Mat l ab 下建立整個抽取濾波器的模型,用Matlab工具包生成 ∑-Δ調制器的輸出信號進行系統測試,輸出結果如圖13 和圖14 所示。

由于量化噪聲被基本濾除,濾波器的輸出得到所需的正弦信號。對整個抽取濾波器完成VerilogHDL 描述,其中運用了Horner 法則以提高精度,采用CSD 碼對乘系數進行編碼,乘法器直接采用移位和加法實現。最后,選用EP2C8Q208C8 并基于Quartus 工具綜合了整個抽取濾波器,系統共占用FPGA 的LE資源達5 435 個,約占總數的66%。綜合后可得到的最高時鐘頻率為5 5 . 9 5MHz ,并且對Modelsim 下后仿輸出的數據進行了FFT 分析,并計算其相應的信噪比,圖15 為5kHz 信號的FFT輸出結果。

圖13 調制器輸出信號

圖14 濾波器輸出信號

圖15 5kHz 信號FFT 分析結果圖

在0~20kHz 范圍內選擇足夠的頻率點進行測試,測試結果如表3 所示,輸出數據的有效位數均滿足大于15bit 的設計要求。

表3 選取頻率點輸出數據的信噪比

6 結論

本文提出了一種面積小功耗低的數字抽取濾波器的設計。設計結構在過采樣率很高時更能體現出它的優勢。通過適當犧牲CIC 濾波器的阻帶衰減特性以換取精度與硬件資源之間的平衡折衷,面積略有下降而功耗則比經典結構降低了35%;采用多相結構實現補償濾波器和半帶濾波器,均可使其功耗降低近50%,同時半帶濾波器的硬件消耗也有明顯下降。通過FPGA 驗證,改進后的64 倍降采樣抽取數字濾波器可滿足15bi t 精度處理的要求。

電源濾波器相關文章:電源濾波器原理

評論