高速PCB中電源完整性的設(shè)計(jì)

中心議題:

本文引用地址:http://www.104case.com/article/179127.htm* 電源噪聲的起因及分析

* 去耦電容的應(yīng)用

* 電源回路的設(shè)計(jì)

解決方案:

* 電源的分層設(shè)計(jì)來考慮

* 電容與芯片盡可能靠近芯片器件

* 利用電源層和地層作為回路,減少了返回環(huán)路面積

一、引言

隨著PCB設(shè)計(jì)復(fù)雜度的逐步提高,對(duì)于信號(hào)完整性的分析除了反射,串?dāng)_以及EMI之外,穩(wěn)定可靠的電源供應(yīng)也成為設(shè)計(jì)者們重點(diǎn)研究的方向之一。尤其當(dāng)開關(guān)器件數(shù)目不斷增加,核心電壓不斷減小的時(shí)候,電源的波動(dòng)往往會(huì)給系統(tǒng)帶來致命的影響,于是人們提出了新的名詞:電源完整性,簡稱PI(powerintegrity)。當(dāng)今國際市場上,IC設(shè)計(jì)比較發(fā)達(dá),但電源完整性設(shè)計(jì)還是一個(gè)薄弱的環(huán)節(jié)。因此本文提出了PCB板中電源完整性問題的產(chǎn)生,分析了影響電源完整性的因素并提出了解決PCB板中電源完整性問題的優(yōu)化方法與經(jīng)驗(yàn)設(shè)計(jì),具有較強(qiáng)的理論分析與實(shí)際工程應(yīng)用價(jià)值。

二、電源噪聲的起因及分析

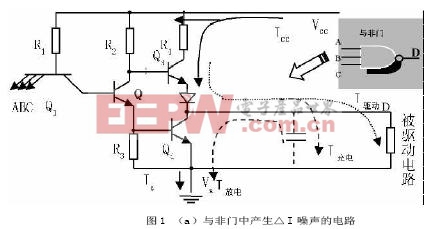

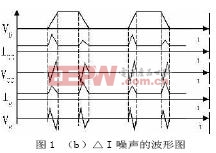

對(duì)于電源噪聲的起因我們通過一個(gè)與非門電路圖進(jìn)行分析。圖1中的電路圖為一個(gè)三輸入與非門的結(jié)構(gòu)圖,因?yàn)榕c非門屬于數(shù)字器件,它是通過“1”和“0”電平的切換來工作的。隨著IC技術(shù)的不斷提高,數(shù)字器件的切換速度也越來越快,這就引進(jìn)了更多的高頻分量,同時(shí)回路中的電感在高頻下就很容易引起電源波動(dòng)。如在圖1中,當(dāng)與非門輸入全為高電平時(shí),電路中的三極管導(dǎo)通,電路瞬間短路,電源向電容充電,同時(shí)流入地線。此時(shí)由于電源線和地線上存在寄生電感,我們由公式V=LdI/dt可知,這將在電源線和地線上產(chǎn)生電壓波動(dòng),如圖2中所示的電平上升沿所引入的ΔI噪聲。當(dāng)與非門輸入為低電平時(shí),此時(shí)電容放電,將在地線上產(chǎn)生較大的ΔI噪聲;而電源此時(shí)只有電路的瞬間短路所引起的電流突變,由于不存在向電容充電而使電流突變相對(duì)于上升沿來說要小。從對(duì)與非門的電路進(jìn)行分析我們知道,造成電源不穩(wěn)定的根源主要在于兩個(gè)方面:一是器件高速開關(guān)狀態(tài)下,瞬態(tài)的交變電流過大;

評(píng)論