串行A/D與FPGA在微型數據記錄儀中的應用

ADS8341轉換的基本時序如圖1所示。本文引用地址:http://www.104case.com/article/178866.htm

由圖1可以看出,ADS8341完成一次轉換需要24個DCLK時鐘,其中在前8個時鐘的上升沿,DIN控制字輸入,控制字輸入完成后,在DCLK的上升沿時刻,BUSY信號輸出一個高電平,在這個時鐘的下降沿,轉換數據按位輸出。經過一次完整的轉換后,在第25個時鐘上升沿,DIN可以再次輸入控制字高位,保證了當DCLK外部時鐘取得最高頻率2.4 MHz時,A/D轉換器的頻率達到最高100 ksa/s。

2 基于FPGA的ADS8341控制器設計

本記錄儀系統記錄采集信號的頻率范圍500Hz以下,在系統實際應用中,對被測信號采用過采樣方式,采樣頻率為被采集信號頻率的5~10倍。系統采用A/D轉換器3通道快速循環采樣,近似實現了通道同步采樣,是一種準同步采樣的方式。經過72個DCLK周期,實現了CH0~CH2通道的順序切換,當A/D轉換器以最大采樣頻率100 ksa/s工作時,記錄儀系統采樣的頻率相當于單通道頻率的1/3,通道1與通道3之間同步誤差最大為48clk,如圖2所示,最小誤差時間約為![]() (此時采樣頻率最快),滿足系統對較低頻率信號采集的要求。

(此時采樣頻率最快),滿足系統對較低頻率信號采集的要求。

系統采用了基于FLASH架構的Actel公司ProASIC3系列A3P100,使用Libero集成開發環境,FPGA的A/D控制模塊主要包含以下功能:

●時鐘控制器

記錄儀系統FPGA的外部時鐘頻率為48 MPa,對系統時鐘20分頻得到時鐘DCLK即可提供A/D轉換器的最大工作時鐘。另外通過邏輯控制,時鐘控制器提供幾個低于2.4 MHz的時鐘頻率,系統可以選擇更低的采樣頻率。

●不等占空比時鐘

本系統設計A/D控制模塊中引入clk_div時鐘信號,占空比為2:3,做為din的控制電平,當clk_div信號為低電平時,din輸出數據,clk _div信號為高電平,din為低電平。

clk_div撐(.duty_factor(duty_factorl),counter_top(counterl)).div_clkl(.reset(clk1_reset),.clk_in(clk_in1),clk_out(clk_out1));//任意占空比分頻時鐘模塊調用

●控制字狀態機

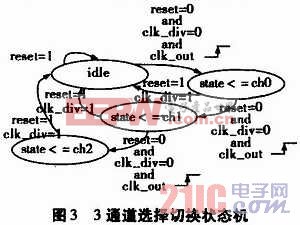

記錄儀上電以后的工作狀態為3個通道循環采樣,控制字狀態發生器循環生成chO=“1001_1111”,ch1=“101_1111”,ch2=“1010_111 1”,并將控制字轉換成串行數據從din引腳輸出,實現A/D轉換器通道切換。

評論