一種12位50 MS/s CMOS流水線A/D轉換器

為了避免零極點對的影響,應該使輔助運放的單位增益帶寬(Waux)滿足:

式中:Wc為主放大器構成的反饋環路的環路單位增益帶寬;Wp2為主放大器構成的反饋環路的非主極點頻率。

考慮到輔助運放的負載電容較小,可以使用較小的驅動電流。設計中,取輔助運放是主運放電流的1/8。整體運放使用開關電容共模反饋穩定輸出共模電壓。表1列出了第1級使用的運算放大器的幾個主要參數,其余運放根據所在級的等效負載電容按比例減小偏置電流。本文引用地址:http://www.104case.com/article/178824.htm

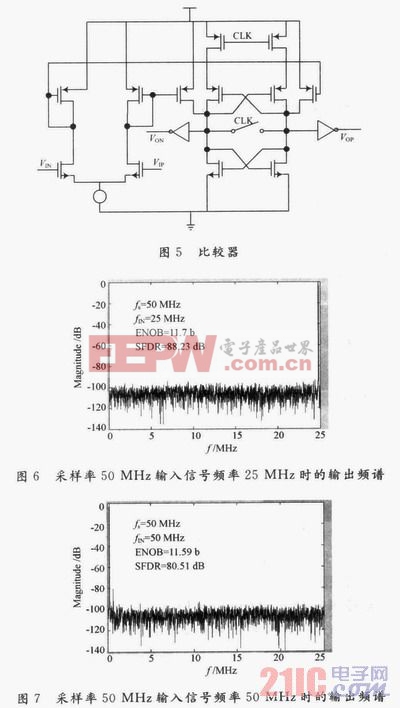

2.3 比較器

使用數字校正技術可以放寬對比較器失調電壓的要求,簡化比較器的設計。設計的比較器由3級組成:預防大級,重建鎖存器和輸出級,如圖5所示。使用預防大級,可以減小傳輸延時。由于預放大器的增益不需要很大,使用40μA的尾電流,這樣可以減小整個比較器的靜態功耗。在CLK為高時,輸出端箍位于閾值附近,在CLK變為低后,重建鎖存器形成正反饋環路,將預放大級輸出的電壓差不斷放大,直至將輸出分別拉到電源和地。輸出級采用反相器,提升比較器的驅動能力與避免亞穩態效應。

3 結果與分析

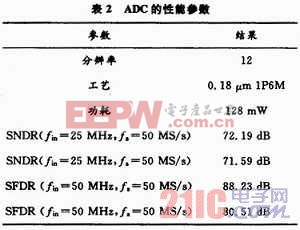

為了驗證ADC的性能,在ADC的輸入端加入單一頻率的正弦波,并對輸出波形進行傅里葉分析。圖6是采樣頻率是50 MHz,輸入25 MHz正弦波時的輸出頻譜圖。此時電路的SNDR=72.19 dB,SFDR=88.23 dB,對應ENOB=11.70 b。圖7是輸入50MHz正弦波時,輸出信號的頻譜圖,此時電路的SNDR=71.59,SFDR=80.51 dB對應ENOB=11.59 b。可見,通過取消SHA和匹配ADC的兩條通道的時間常數,在輸入低頻和高頻信號時ADC始終具有較好的線性度。在采樣頻率時50 MHz時,ADC的功耗為128 mW(不含參考電壓產生電路)。表2列出了ADC的主要性能參數。

4 結語

設計了一個12位50 MS/s的流水線ADC,該電路使用0.18μm 1P6M工藝實現。通過取消前端采樣保持電路,消除了采樣保持電路引起的失真和帶來的功耗開銷;經過仔細匹配輸入時間常數,保證ADC在輸入高頻信號時依然保持足夠線性度;使用運放縮減技術,進一步辟低了功耗。仿真結果表明,該ADC滿足設計要求。

評論