基于VHDL的異步FIFO設計

仔細觀察表1并分析數據,一種新穎的判斷空滿標志的方法為:當讀/寫指針的最高位(MSB)不相等且讀/寫指針的次高位不相等,剩余的N-2位地址相等時,此時寫指針追上了讀指針,即寫指針比讀指針多轉一圈,狀態模塊輸出滿標志;當讀/寫指針N+1位都相等時,狀態模塊輸出空標志。判斷滿標志部分的VHDL代碼:

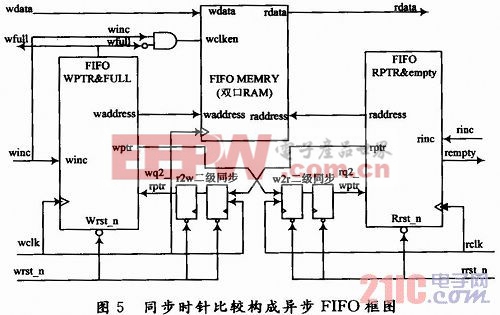

3.4 異步FIFO總體設計

通過時針比較產生的異步FIFO框圖如圖5所示。WCLK和RCLK分別為讀時鐘和寫時鐘,wrst_n和rrst_n分別為讀/寫模塊的復位信號。 rdata為數據輸出端口,wdata為數據輸入端口。異步FIFO通過讀/寫指針來尋址一個雙口RAM來實現對數據的讀/寫,雙口RAM的大小為2nB。讀指針被二級同步鏈到寫時鐘域,然后與寫時針比較產生滿標志,讀指針產生讀地址raddress;寫時針被二級同步鏈同步到讀時鐘域,然后與讀時鐘比較產生空標志,寫指針產生寫地址waddress。需要注意的是此異步FIFO設計中,空滿標志是保守的空滿標志,比如滿標志,當讀時針通過二級同步鏈同步到寫時鐘域且滿足滿標志的條件時,寫指針停止加1操作,而同步讀指針的過程中,讀時針則移動到了其他的地址,同樣的適合于空標志,當輸出空,滿時,其實FIFO的真實狀態是還有空間沒被寫滿或者讀空,這就是保守的空和滿,而這正保證了FIFO不會向上會向下溢出,進一步提高了FIFO工作的可靠性。本文引用地址:http://www.104case.com/article/178738.htm

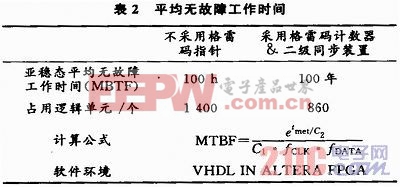

表2為平均無故障工作時間的對比,C1和C2依賴于器件工藝。

4 結語

一個高的平均無故障工作時間表明一個設計是優秀的,提高亞穩態的平均無故障工作時間減少信號傳輸中導致亞穩態問題的風險。本文通過研究FIFO的基本結構以及FPGA亞穩態的產生機理,提出了利用二級同步鏈和格雷碼計數器指針解決了同步以及空滿狀態判斷的難題,給出了VHDL軟件代碼,且該設計已經通過QuartusⅡ的時序仿真驗證,作為獨立模塊可以應用到需要異步時鐘域傳輸數據的電路中,大大提高異步數據傳輸效率及平均無故障工作時間。

評論