基于VHDL的異步FIFO設計

摘要:FIFO經常應用于從一個時鐘域傳輸數據到另一個異步時鐘域。為解決異步FIFO設計過程中空滿標志判斷難以及FPGA亞穩態的問題,提出一種新穎的設計方案,即利用格雷碼計數器(每次時鐘到來僅有1位發生改變)表示讀/寫指針,設計二級同步鏈為跨越不同時鐘域的讀/寫指針,以提供充足的穩定時間,并通過對比格雷碼指針產生空滿標志位。該設計采用VHDL語言進行設計,利用ALTERA公司的FPGA得以實現。經驗證進一步表明,模塊化的設計不僅避免了亞穩態的產生,增大平均無故障工作時間(MBTF),也使工作效率大為提升。

關鍵詞:FIFO;異步;亞穩態;格雷碼

先進先出緩存電路讀/寫(FIFO)在大規模邏輯設計中被廣泛應用,幾乎每個芯片都要涉及,同樣在空空導彈的數據傳輸體系中也得以大量應用。FIFO類型可以分為兩種,第一種為同步FIFO,即讀/寫時鐘是同步的,這里的同步不僅僅是指讀/寫時鐘為同一個時鐘,即屬于同一個時終域。當讀/寫時鐘頻率為倍數關系,即相位關系確定時,也歸屬同步FIFO的范疇。另一種為異步FIFO,讀/寫時鐘頻率不成倍數關系或相位關系不確定,即跨時鐘域。異步FIFO可以在不同的時鐘域之間快速方便地傳輸實時數據,因此在遙測數據傳輸中,異步FIFO實用性更好。然而如何正確地產生空滿標志以及如果解決亞穩態問題是異步FIFO設計的難點。

1 FIFO結構

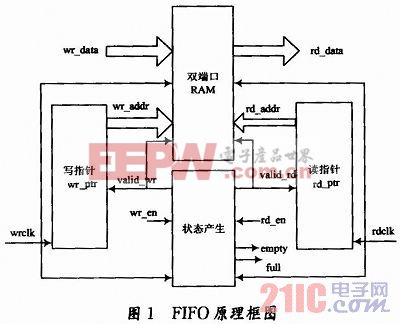

首先,典型的FIFO結構框圖如圖1所示。FIFO的數據存儲在具有獨立寫端口和讀端口的RAM中。讀指針r0_pointer指向下一個將要讀取的位置,寫指針wrpointer指向下一個將要寫入的位置,每1次寫操作后寫指針加1,讀操作使讀指針加1。狀態產生模塊中,full和empty表示FIFO讀/寫的臨界狀態。FIFO設計的關鍵是產生讀/寫地址和空滿標志。空滿標志是基于引起指針相等的操作。如果是復位或者讀操作引起

讀/寫指針相等,FIFO認為是空;如果原因是寫操作,那么FIFO認為是滿。異步FIFO設計的難點是如何同步跨時鐘域的指針以及空滿標志的產生。

2 亞穩態

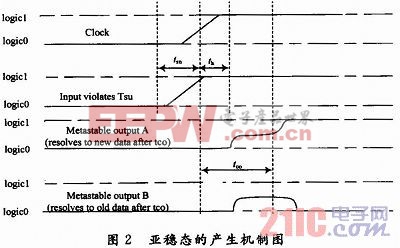

亞穩態是當信號在無關的電路中或異步時鐘域之間傳輸時導致FPGA系統失效的一種現象。包括FPGA在內的所有數字器件的寄存器都定義了信號時序要求,以保證每一個寄存器都能夠從輸入端獲取數據和在輸出端產生數據。為了確保可靠的操作,輸入信號必須在時鐘沿之前穩定一段時間(寄存器建立時間tsu),并且在時鐘沿之后穩定一段時間(寄存器保持時間th),然后寄存器輸出經過一個特定的時鐘到輸出延時后有效。滿足此要求寄存器才可以正確的在輸入端獲取數據在輸出端產生數據,否則輸出有可能是亞穩態。在亞穩態時,寄存器的輸出電壓在高低電平之間搖擺,即輸出將有可能是邏輯0(0 V)或者邏輯1(+5 V),或者是介于0~5 V中間的某個值。亞穩態產生機制圖如圖2所示,當建立時間或者保持時間不滿足時序要求時便會產生亞穩態。

在同步系統中,輸入信號必須總是滿足寄存器時序要求,所以亞穩態不會發生。亞穩態問題通常發生在當一個信號在無關的線路中或異步時鐘域中傳輸。一個寄存器進入亞穩態和從亞穩態進入穩態的時間依賴于制造商的制造工藝和使用環境。大部分情況下,寄存器會很快的進入一個定義的穩態中。在異步FIFO設計中就要避免亞穩態的產生。

評論