一種DC/DC變換器中差分延遲線ADC的實現

摘要:文中介紹了一種無需外部時鐘、可抵消部分工藝偏差的差分延遲線ADC,并對其建模。該ADC結構簡單、控制信號在內部產生、轉換速率快、功耗低,可應用在高頻數字DC/DC控制芯片中。在0.13μmCMOS工藝下仿真表明,在采樣電壓0.7~1.5V范圍內,該ADC輸出沒有明顯偏移,線性度良好。

本文引用地址:http://www.104case.com/article/178684.htm傳統的DC/DC變換器一般采用模擬控制方式,它具有體積小,功耗低等優點,但易受噪聲影響。而數字控制的DC/DC變換器對工藝參數和環境不敏感、控制算法可通過編程實現、易于集成,且能大大縮短產品的開發周期。

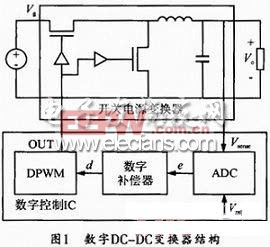

1 DC/DC變換器結構

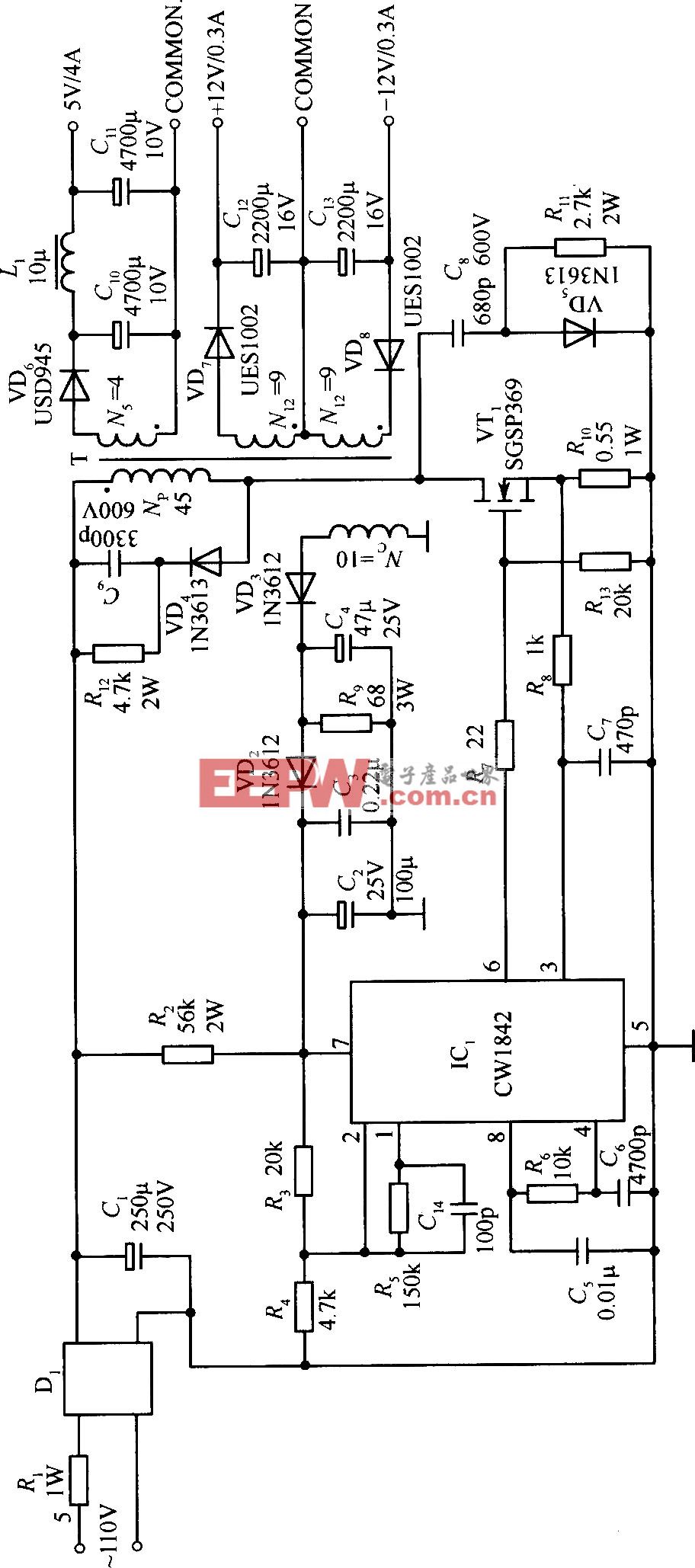

數字控制器主要由模數轉換器(ADC)、數字補償器(Digital Compensator)和數字脈沖寬度調制器(DPWM)組成。一種常用的數字控制器如圖1所示。主電路輸出電壓與基準電壓經ADC進行比較并轉換為相應的數字誤差信號,數字補償器則根據誤差進行補償得到給定數字信號。經DPWM轉換成時間信號,控制主電路開關通斷。

2 延遲線ADC

標準CMOS工藝下一個邏輯門延遲td與電源電壓VDD叻有這樣一個關系

其中,K是一個與器件和工藝有關的常數,Vth是MOS器件的閾值電壓。當VDD大于Vth時,td可看作與VDD成反比。

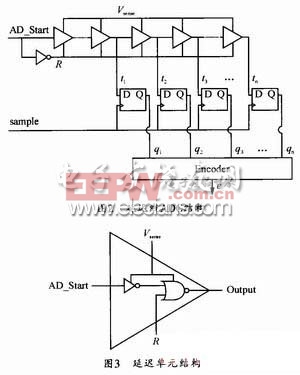

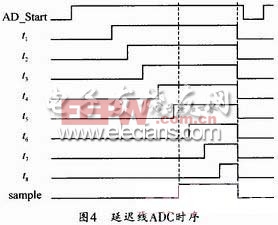

延遲線ADC由延遲鏈、寄存器組和譯碼電路組成,結構如圖2所示。一串延遲單元組成延遲鏈。一種可行的延遲單元的結構如圖3所示。它由一個反相器與一個或非門級聯得到。每個延遲單元都有一個輸入端,一個復位端和一個輸出端。

給定一個開始信號AD_Stan,經一定時間間隔后產生一個采樣脈沖信號sample,作為D觸發器的控制信號。在采樣信號有效時對D觸發器的輸入信號進行鎖存,將D觸發器的輸出信號送至譯碼電路得到最后的誤差信號。圖4是延遲線ADC的時序圖,假設圖2中n=8。在采樣信號有效時,AD_Start信號正好傳到第5個延遲單元,于是q1~q5輸出為1,q6~q8輸出為0。采樣電壓越大,延遲時間td越小,信號傳播得越快,輸出的溫度計碼中的1的個數越多。譯碼電路再將溫度計碼轉換為所需要的二進制碼。延遲線ADC即通過輸入電源對延遲鏈供電,根據延遲鏈延遲時間的大小來確定輸入的大小。

評論