一種低溫漂的CMOS帶隙基準電壓源的研究

1.2 帶隙基準電壓源總體電路

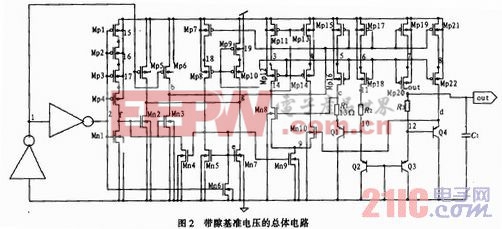

帶隙基準電壓源總體電路總共由4部分組成:A部分是啟動電路,B部分提供偏置電壓,C部分是運算放大器,D部分是帶隙電壓源的核心部分。其中核心部分是由雙極晶體管構成,實現了VBE和VT的線性疊加,獲得近似零溫度系數的輸出電壓。總體電路如圖2所示。本文引用地址:http://www.104case.com/article/178425.htm

1.3 運放的失調對基準源的影響

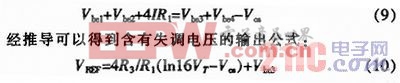

基準源中運放的設計是非常重要的,運放的失調是基準源的一個主要誤差源。由于不對稱性,運放會受到輸入失調的影響。假設失調電壓為Vos,經計算得到含失調電壓的輸出公式為:

可見,Vos的大小可能導致相當大的基準源輸出電壓誤差。此外,Vos自身是溫度的函數,和理想運算放大器相比,會引入一定的誤差,而由運算放大器電源抑制比PSRR引入的誤差可以折合成失調輸入電壓Vos也將和電源有關。這樣,為了減小失調對基準電壓的影響,運放的失調就要盡可能地小。然而,引起失調的原因有許多,如晶體管之間的不匹配、運放輸入級管子閾值電壓的不匹配、運放的有限增益等等。因此,實際上,Vos是很難完全消除的,但通過提高運放的增益和細致地設計版圖可以減小它對基準電壓的影響,提高基準電壓源的精度。

1.4 電源抑制比

電源抑制比(PSRR)是電路對電源電壓頻率變化的抑制能力,是從運放的輸入到輸出的開環增益與從電源到運放輸出的增益之比,用KPSR表示。對帶隙基準而言,由于輸出電壓和Vdd無關,所以Vdd的變化基本上不會影響輸出參考電壓的影響。但是隨著工作頻率的提高,由于電容耦合的原因導致輸出電壓在高頻時會受到Vdd的波動的影響,從而影響輸出電壓的穩定性。具體的電路設計中考慮了這一點,在電路中采用了自偏壓cascode結構的電流鏡,同時在輸出端接一對地濾波電容,輸出電壓的電源抑制特性就得到了很好的提高。

1.5 啟動電路

啟動電路也是帶隙基準源中一個重要的部分。如圖2中A部分所示,電路可能會出現零輸出的情況。因為放大器兩端的輸入都為零電平時,電路處于一種不工作狀態,因此需要一個啟動電路來打破這種平衡。圖中引入的啟動電路由Mp1~Mp6和Mn1~Mn4組成。其工作原理是由Mp1~Mp4,Mn1組成的反向器驅動Mn2和Mn3,使Mn2和Mn3導通,從而通過a點和b點間接給運算放大器的兩個差分輸入端提供偏置電壓,保證在系統加電的時候,輸入差分對不會關斷,當電路正常工作后,啟動電路關斷。

2 仿真結果

2.1 溫度特性

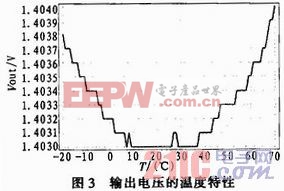

該電路的仿真基于Chartered 0.25 μm models。仿真軟件是T—SPICE,電源電壓為3.3 V,R3/R1的比值為2.306 6,這樣的結果在版圖設計中比較容易實現,可以采用單元電阻串連的形式,有利于減少因為版圖失配引起的誤差。單元電阻的W=3μm,L=10 μm,方塊電阻R=330 Ω,采用的第一層多晶實現。圖3所示的是輸出電壓溫度特性的仿真結果。

溫度在-20~70℃之間變化,輸出電壓溫度特性如圖3所示,它的溫度系數約為10 ppm/℃。因此,可以看出輸出電壓的溫度特性并不是一直都為零,而是在一個溫度范圍內為零,在其他溫度下為正值或者負值。這是由于基極一發射極電壓、集電極電流、失調電壓以及電阻隨溫度變化引起的。

評論