一種緊湊型全橋DC-DC隔離電源設計

2 實驗結果

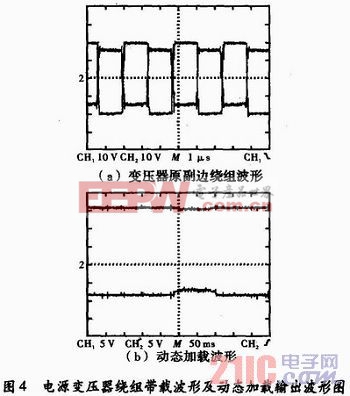

圖4(a)所示為實際全橋DC-DC電源變壓器原邊及副邊繞組帶載波形,其中CH1為原邊線圈兩端電壓,CH2為副邊線圈正電壓。由于器件分散性,實際測試DC-DC電源工作頻率為366 kHz,頻率偏差為3.8%,滿足設計要求。圖4(b)所示為動態加載輸出波形,其中CH1為輸出正電壓,CH2為輸出負電壓。測試時負載為35 Ω/10 W,可以看到突加突卸額定負載時輸出正電壓較平穩,波動1 V,滿足設計要求;負電壓稍有波動,考慮到IGBT負壓是用來維持關斷狀態,負壓在-5~-15 V即可,因此滿足半橋集成驅動電源的要求。本文引用地址:http://www.104case.com/article/178304.htm

3 結束語

針對綠色能源設計需求,結合集成驅動板具體使用條件,實現了DC-DC隔離電源高效、可靠設計,并且易于和IGBT模塊集成,易于安裝。該電路以兩組磁芯原邊繞組共用高頻全橋開關的DC-DC隔離電源;生成4路無需隔離的全橋脈沖信號,實現了高功率密度的板上電源的緊湊設計。仿真和實驗結果表明,該電源電路簡潔、高效、可靠,達到了預期目的。

評論