一種基于動態閾值NMOS的1.2V CMOS模擬乘法器

摘要 分析了以動態閾值NMOS晶體管作為輸入信號的輸入晶體管,利用4個動態閾值NMOS和2個有源電阻設計和實現的一種1.2 V低功耗CMOS模擬乘法器電路。該電路具有節省輸入晶體管數目、偏置晶體管和偏置電路,以及性能指標優良的特點。其主要參數指標達到:一、三次諧波差值40 dB,輸出信號頻帶寬度375 MHz,平均電源電流約30μA,動態功耗約36μW。可直接應用于低功耗通信集成電路設計。

關鍵詞 模擬乘法器;動態閾值晶體管;低壓;低功耗;金屬氧化物半導體

隨著便攜式電子產品的不斷發展,以及各國對節能的嚴格要求,低功耗集成電路及電子系統已經成為技術發展的方向之一,而低電源電壓是實現低功耗最直接有效的方法,其中CMOS模擬集成電路的低壓低功耗設計是實現低壓低功耗集成電路的難點。模擬乘法器作為模擬電路中最基本的電路之一,在自適應濾波器、頻率倍增器、各種調制解調器等電子系統中具有廣泛的應用。傳統的模擬乘法器—般采用Gilbert結構實現,由于電源到地的通路上至少有3~4個晶體管,沒有辦法實現低壓低功耗,必須采用新的電路結構實現。

采用動態閾值NMOS晶體管作為兩路輸入信號的輸入晶體管,節省了輸入晶體管和偏置晶體管的數目,實現了低壓低功耗的目的。文中首先對動態閾值NMOS晶體管的特性進行了系統分析,包括跨導、頻率特性等,再提出了一種基于動態閾值NMOS晶體管的1.2 V CMOS模擬乘法器,并進行了性能分析,采用Hspice進行了各種參數的仿真,對仿真結果進行了比較分析和討論。

1 動態閾值NMOS晶體管

所提出的動態閾值NMOS晶體管的工藝基礎是傳統標準雙阱CMOS工藝或P阱CMOS工藝,其特點是兩個輸入信號同時加到NMOS的柵極(G)和襯底(B)端,即輸入電壓為VGS和VBS,不需要引入特殊的工藝步驟。當NMOS的VBS=0時,就是常用的準恒定閾值電壓增強型NMOS晶體管,如果VGS和VBS同時在變化,而VBS的變化直接會影響VTH(N)變化。式(1)是當VGS一定時,NMOS閾值電壓VTH(N)與VBS的關系,表明當VBS增大時,VTH(N)會隨之減小,所以動態閾值是實現CMOS模擬電路低壓化的理想技術之一。

![]()

其中,VTH0(N)是VBS=0時的NMOS閾值電壓,φF為表面電動勢,γ為體效應因子。

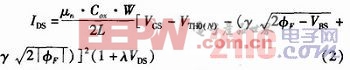

當動態閾值NMOS晶體管滿足VDS≥VGS-VTH(N)時,即晶體管工作在飽和區,IDS與VGS、VBS之間的關系如式(2)所示。

基于CSMC 0.6 μm DPDM CMOS工藝的BSIM3V3 Spice模型,采用Hspice進行仿真,以驗證動態閾值NMOS晶體管的V-I特性。圖1為不同VBS條件下的VDS~IDS關系曲線VGS=1.2 V,自下而上5條曲線所對應的VBS分別為0 V、0.3 V、0.6 V、0.9 V和1.2 V,表明在相同VDS條件下IDS隨著VBS的不斷增大而增大。圖2為不同VGS條件下的VBS~IDS關系曲線VDS=1.2 V,自下而上7條曲線所對應的VGS分別為0 V、0.2 V、0.4 V、0.6 V、0.8 V、1.0 V和1.2 V,其中VGS為0 V、0.2 V、0.4 V的3條曲線由于IDS數值太小,已與橫坐標幾乎重合,圖2表明在相同VBS條件下IDS隨著VGS的不斷增大而增大。

將式(2)分別對VBS和VGS求偏導,即可以得到

![]()

由于體效應因子γ的值較小,所以gmbsgm,但VBS的增加,則可以增加gmbs。

評論