電源完整性設計2

你可能會說,只用一個容值,只要并聯電容數量足夠多,也能達到同樣低的阻抗。的確如此,但是在實際應用中你可以算一下,多數時候,所需要的電容數量很大。真要這樣做的話,可能你的電路板上密密麻麻的全是電容。既不專業,也沒必要。

選擇電容組合,要考慮的問題很多,比如選什么封裝、什么材質、多大的容值、容值的間隔多大、主時鐘頻率及其各次諧波頻率是多少、信號上升時間等等,這需要根據具體的設計來專門設計。

通常,用鉭電容或電解電容來進行板級低頻段去耦。電容量的計算方法前面講過了,需要提醒一點的是,最好用幾個或多個電容并聯以減小等效串聯電感。這兩種電容的Q值很低,頻率選擇性不強,非常適合板級濾波。

高頻小電容的選擇有些麻煩,需要分頻段計算。可以把需要去耦的頻率范圍分成幾段,每一段單獨計算,用多個相同容值電容并聯達到阻抗要求,不同頻段選擇的不同的電容值。但這種方法中,頻率段的劃分要根據計算的結果不斷調整。

一般劃分3到4個頻段就可以了,這樣需要3到4個容值等級。實際上,選擇的容值等級越多,阻抗特性越平坦,但是沒必要用非常多的容值等級,阻抗的平坦當然好,但是我們的最終目標是總阻抗小于目標阻抗,只要能滿足這個要求就行。

在某個等級中到底選擇那個容值,還要看系統時鐘頻率。前面講過,電容的并聯存在反諧振,設計時要注意,盡量不要讓時鐘頻率的各次諧波落在反諧振頻率附近。比如在零點幾微法等級上選擇0.47、0.22、0.1還是其他值,要計算以下安裝后的諧振頻率再來定。

還有一點要注意,容值的等級不要超過10倍。比如你可以選類似0.1、0.01 、0.001這樣的組合。因為這樣可以有效控制反諧振點阻抗的幅度,間隔太大,會使反諧振點阻抗很大。當然這不是絕對的,最好用軟件看一下,最終目標是反諧振點阻抗能滿足要求。

高頻小電容的選擇,要想得到最優組合,是一個反復迭代尋找最優解的過程。最好的辦法就是先粗略計算一下大致的組合,然后用電源完整性仿真軟件做仿真,再做局部調整,能滿足目標阻抗要求即可,這樣直觀方便,而且控制反諧振點比較容易。而且可以把電源平面的電容也加進來,聯合設計。

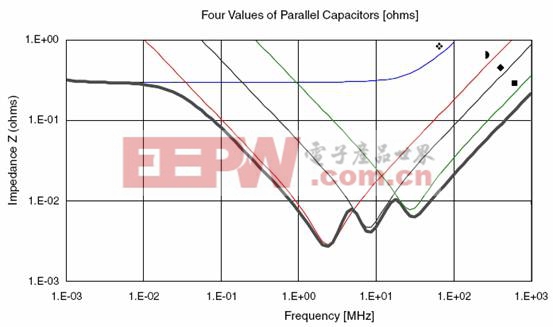

圖13是一個電容組合的例子。這個組合中使用的電容為:2個680uF鉭電容,7個2.2uF陶瓷電容(0805封裝),13個0.22uF陶瓷電容(0603封裝),26個0.022uF陶瓷電容(0402封裝)。圖中,上部平坦的曲線是680uF電容的阻抗曲線,其他三個容值的曲線為圖中的三個V字型曲線,從左到右一次為2.2uF、0.22uF、0.022uF。總的阻抗曲線為圖中底部的粗包絡線。

這個組合實現了在500kHz到150MHz范圍內保持電源阻抗在33毫歐以下。到500MHz頻率點處,阻抗上升到110毫歐。從圖中可見,反諧振點的阻抗控制得很低。

圖13 設計實例

小電容的介質一般常規設計中都選則陶瓷電容。NP0介質電容的ESR要低得多,對于有更嚴格阻抗控制的局部可以使用,但是注意這種電容的Q值很高,可能引起嚴重的高頻振鈴,使用時要注意。

評論