PCB板時鐘電路的電磁兼容設計

2.2 時鐘頻率對輻射的影響

假設有2個時鐘信號,幅度都為1 V,上升時間都為3.33 ns,重復頻率為30 MHz和90 MHz,根據上面的傅里葉變換可以得到2個時鐘信號的頻譜分布,如圖2和圖3所示。

2.3 時鐘頻譜的比較

從圖1可以看出,時鐘諧波干擾尤其是高次諧波干擾的強度會隨著上升和下降時間的降低而大大加強,2 ns上升時問的時鐘的高次諧波比4 ns上升時間的對應諧波高出1~2倍。

當上升下降時間相同時,周期T(或者基頻f)的高低對時鐘產生的高次諧波干擾的影響非常大,圖2和圖3分別是重復頻率30MHz和90MHz,上升時間都為3.33 ns,幅度為1 V的梯形時鐘波諧波干擾的大小。從圖中可以看出,2種時鐘在270 MHz的諧波干擾,90 MHz時鐘在270 MHz(3次諧波)的諧波干擾比30 MHz時鐘在270 MHz(9次諧波)的諧波干擾高出15 dB左右;再比較90 MHz時鐘在810 MHz(9次諧波)的諧波干擾比30MHz時鐘在810 MHz(27次諧波)的諧波干擾高出12 dB左右。

因此在進行時鐘系統設計時,在條件允許的情況下優先選用較低的時鐘頻率,比如在設計以太網的PHY芯片時既有采用125 MHz外部時鐘的也有采用25 MHz外部時鐘的,如果在其他技術條件允許應優先選用外部時鐘為25 MHz的芯片,而且在各方面技術條件都滿足的情況下優先選擇上升和下降時間比較長的時鐘或者時鐘驅動電路。

3 時鐘電路的電磁兼容設計

在PCB板上實現時鐘電路的電磁兼容設計主要從下面的幾個方面來考慮:時鐘晶振及其驅動器的電源處理;在PCB板上晶振及其驅動器的下面做局部的覆銅處理;時鐘信號線的布線;時鐘信號的端接和濾波等。

3.1 電源設計

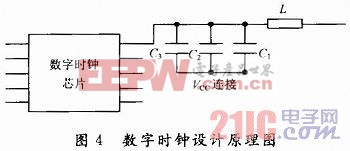

當時鐘電路的輸出同時發生狀態變換時,會對電源系統產生較大的瞬態電流,或灌電流,為了避免時鐘芯片對單板電源系統的沖擊,抑制單板電源的電磁干擾,就需要對時鐘電源部分進行濾波和隔離設計。其設計原理圖如圖4所示。本文引用地址:http://www.104case.com/article/177763.htm

3.2 鋪銅及布線設計

晶體振蕩器內部的電路會產生射頻電流,如果晶體是金屬外殼封裝的,直流電源腳是直流電壓參考和晶體內部射頻電流回路參考的依據。不同的晶體(CMOS,TTL,ECL等)內部產生的射頻電流對金屬外殼的輻射大小不同,如果晶體金屬外殼不與大的地平面連接,則不能將晶體金屬外殼上大的瞬態電流瀉放到地平面上。

在晶振和時鐘電路下面的局部地平面可以為晶振及相關電路內部產生的共模RF電流提供通路,從而使RF發射最小。為了承受流到局部地平面的共模RF電流,需要將局部地平面與系統中的其他地平面多點相連。即表層的局部地平面與系統內部地平面相連的過孔提供了到地的低阻抗。同時要注意的是要保證晶振底下地平面的完整性。使用完整地平面的信號的回流和信號本身方向相反,大小相等,能夠很好的互相抵消,可以保證其良好的信號完整性和電磁兼容特性。但是,如果地平面不完整,回流路徑中的電流與信號本身的電流不能相互抵消時(盡管這種電流不平衡有時候是不可避免的),就會產生一部分共模電流。產生的共模電壓就會激勵連接的外圍結構,造成較大的輻射。

如果布線從晶振下面穿過,特別是傳輸到連接器的布線,不僅破壞局部地平面的作用,而且還會將晶振產生的噪聲通過容性耦合的方式耦合到穿過它下面的信號線,使這些信號線帶有共模電壓噪聲,如果這些信號線通過連接器又延伸出PCB,就會將噪聲帶出。這是一種典型的共模輻射問題,原理如圖5所示。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論