一種基于開關邏輯結構的低功耗SAR ADC的設計

3 電路仿真與芯片測試

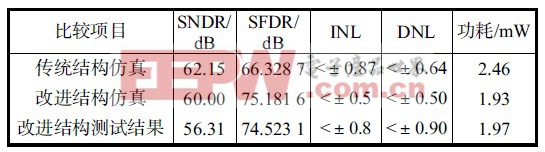

利用Cadence AMS作為仿真工具,對SAR ADC進行了功能仿真,采用FFT 法分析ADC 的動態(tài)性能,得到的頻譜圖如圖4 所示。仿真所得信噪失真比(SNDR)為60.472,dB.

圖4 電路仿真的FFT頻譜

基于Chartered 0.35,μm,2P4M 工藝,完成了電路的版圖設計,其中單位電容均采用工藝偏差相對較小的poly-poly 電容。圖5 給出了經MPW 流片SARADC 芯片圖。由于電路的非線性與電路的元件匹配有關,其匹配性越好,其線性度越高,因此版圖設計中采用了一系列手段以提高電容陣列的匹配性,包括采用共質心結構布置版圖,降低因芯片面積加大帶來的氧化層梯度的影響;電容陣列周邊采用虛擬結構;單位電容采用固定的周長/面積比等。對比表1中的無失真動態(tài)范圍參數,可以看出線性度提高了11.78%.

圖5 SAR ADC芯片

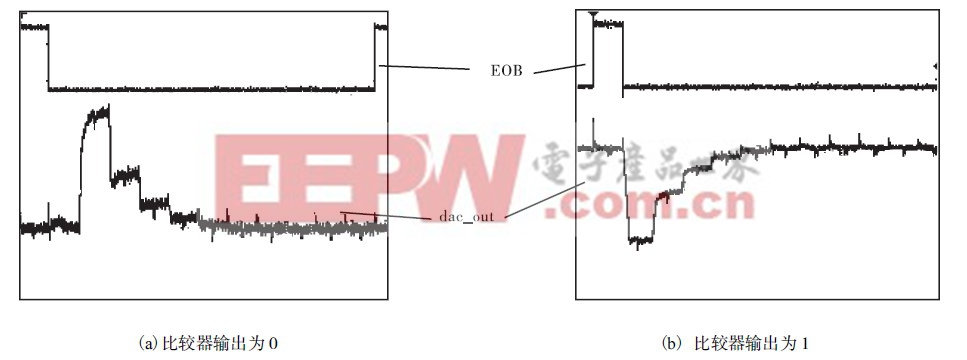

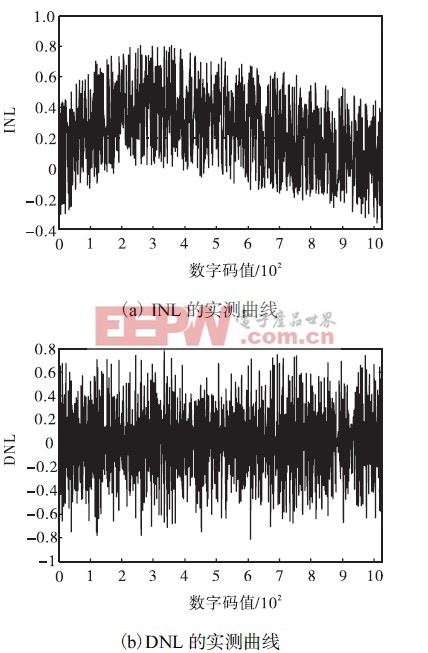

使用TeKtronix TLA5204B 邏輯分析儀和TDS3052B 示波器等工具對MPW 流片回來的芯片進行了測試。圖6 給出了D/A 的測試結果,其中EOB 為轉換結束信號,dac_out 為D/A 輸出信號;SAR ADC在250,kHz 的轉換速率下的實測積分非線性(Integralnonlinearity,INL)誤差和微分非線性(differnetialnonlinearity,DNL)誤差特性曲線[14]如圖7 所示。

圖6 D/A的測試結果

圖7 SAR ADC的INL和DNL的實測曲線

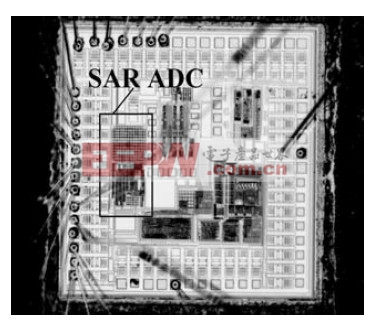

表1 顯示了10 位SAR ADC 的整體性能。比較流片后測試結果和仿真結果可見所設計的SAR ADC較好地達到了低功耗的設計要求,性能良好。

4 結 語

完成了一款基于開關邏輯結構的SAR ADC 設計。其中的D/A 轉換器由溫度計碼的開關邏輯結構來控制,從而減小了開關的動作頻率,降低了整個系統(tǒng)的功耗。測試結果顯示,設計的SAR ADC 實現了10 位模數轉換功能,轉換速率為250 kHz,INL 和DNL 均小于1 個LSB,功耗小于2 mW,表明該電路較好地達到了設計要求。

評論