一種基于開關邏輯結構的低功耗SAR ADC的設計

摘 要:設計并實現了一款10 位逐次逼近型模數轉換器,該電路采用了改進型開關邏輯結構降低了開關的動作頻率,提高了數模轉換器的線性度,同時降低了模數轉換器的功耗。仿真結果表明,該模數轉換器在Chartered 0.35 μm2P4M工藝下實現了10 位精度,轉換速率為250 kHz,信噪比大于60 dB,功耗小于2 mW.流片后測試結果顯示芯片達到設計指標要求,平均功耗為1.97 mW。

本文引用地址:http://www.104case.com/article/177369.htm逐次逼近型模數轉換器(successive approximatiONregiSTer analog-to-digital converter,SAR ADC)是應用于采樣速率低于5,MHz 的中高分辨率的常見結構,其分辨率一般為8~16 位,因制造工藝與現代數字CMOS 工藝的兼容性好,且易于在較低的工藝成本下實現,所以廣泛應用于現代超大規模集成電路與片上系統(system-on-chip,SOC),如便攜式/電池供電儀表、筆輸入量化器、工業控制和數據/信號采集器等。

筆者設計了一款10位低功耗SAR ADC,采用溫度計碼控制的開關邏輯結構代替傳統的開關陣列控制數模(digital-to-analog,D/A)轉換器的動作,從而提高了D/A 轉換器的線性度并降低了ADC 的功耗。ADC 在 250,kHz 的采樣速度下實現了10 位的模數轉換功能,功耗小于2,mW。

1 SAR ADC的結構和工作原理

傳統SAR ADC 的結構主要包括5 個部分,分別是:采樣保持電路、模擬比較器、D/A 轉換器、逐次逼近寄存器和邏輯控制單元。在很多實際電路中,采樣保持與D/A 轉換器合二為一。

SAR ADC 通過比較器對D/A 轉換器產生的參考電壓和采樣所得的模擬輸入電壓進行比較,由逐次逼近寄存器逐次地決定每一位數字碼,直到完成最低有效位(least significant bit,LSB)的轉換。SAR ADC采用二進制搜索算法來決定模數轉化過程中的數字碼值,N 位的SAR ADC需要進行N 步的轉化。

在SAR ADC 中,數字模塊消耗的功耗較小,整個SAR ADC的功耗主要集中在3 個方面。

(1)對采樣保持電容的充放電。

(2)對D/A轉換器中二進制加權電容的充放電。

(3)模數轉換過程中比較器所消耗的功耗。

有關降低SAR ADC 功耗的文獻通常針對以上3個方面來提出電路結構的改進方案,如在數模轉換器中采用特殊結構的電容陣列以及采用功耗較低的動態比較器等。

為了降低ADC 的整體功耗,筆者設計的D/A 轉換器采用了電荷分配型的結構。與其他同類型ADC的最大區別在于用溫度計碼的開關邏輯結構代替了常用的二進制碼開關來控制D/A 轉換器,從而合理優化了電容陣列的開關邏輯結構,減小了開關的動作頻率,既提高了D/A 轉換器的分辨率和線性度,同時又降低了整個系統的功耗。

2 基于開關邏輯結構的D/A轉換器

2.1 D/A轉換器的基本原理

傳統型電荷分配型D/A 轉換器通常由一個二進制加權電容陣列、一個與LSB 等值的電容和開關陣列組成,其轉換過程可以分為3 個階段。

(1)采樣階段:此時,所有電容的上極板接地,下極板接輸入電壓,這樣,上極板存儲了與輸入電壓成正比的電荷,這些電荷在D/A 轉換器的轉換過程中保持不變。

(2)保持階段:此階段,二進制加權電容的上極板接地開關斷開,下極板接地,引起電容陣列上極板的參考電壓的變化。

(3)再分配階段:此時,逐次逼近寄存器的最高位被置為1,即最大的電容2N-1C 的下極板連接到基準電壓Vref,在下一個時鐘周期來臨時,最大的電容的下極板的連接狀態是由比較器的比較結果決定的。同時次大的電容的下極板連接到基準電壓Vref.這個過程將會進行N 次,在每一個時鐘周期內比較器的比較結果決定了原先被試探的電容的下極板接地或是接基準電壓Vref,同時將比試探電容小一半的那個電容設為試探電容,直到整個轉換過程完成,即最小電容的下極板狀態被決定。

2.2 D/A轉換器的低功耗設計

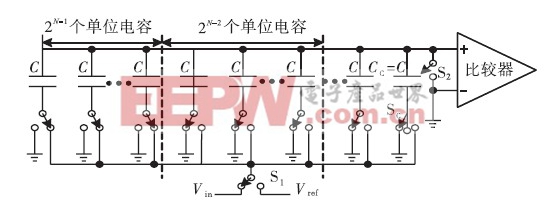

所設計的開關邏輯結構的D/A 轉換器如圖1 所示,其與傳統型D/A 的區別是將二進制加權電容陣列進行了分拆并加入了碼制轉換電路。碼制轉換電路將邏輯控制單元控制的寄存器的輸出二進制碼轉化成為溫度計碼,以溫度計碼來控制整個二進制加權電容陣列,以降低開關動作頻率。

圖1 D/A轉換器

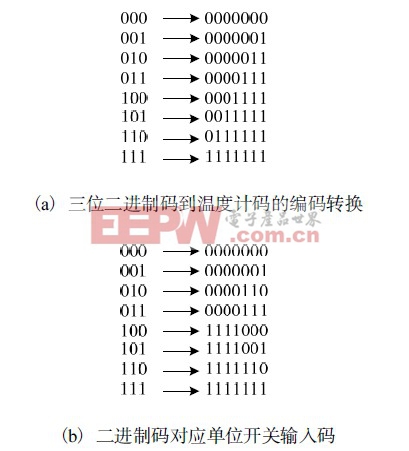

以3 位D/A 轉換器為例來簡要說明。圖2(a)為三位的二進制碼到溫度計碼的編碼轉換圖;圖2(b)為二進制碼對應單位開關輸入碼圖。由圖2 可知,一旦比較器的輸出為0,即在模數轉換過程中出現輸入信號比D/A 轉換器所產生的參考電壓小的情況,采用溫度計碼的開關邏輯結構對減小開關動作頻率是有利的。將二進制碼轉換為溫度計碼只需通過一個簡單的編碼轉換電路就可以實現。

圖2 碼制轉換示意

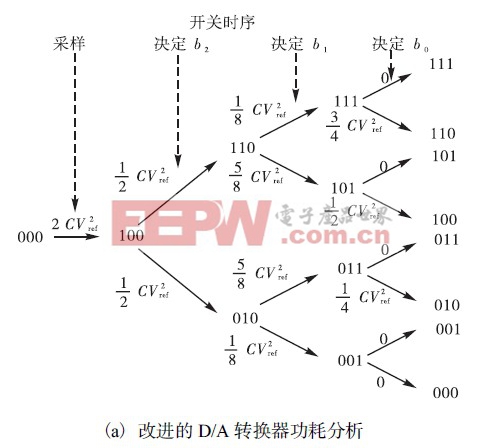

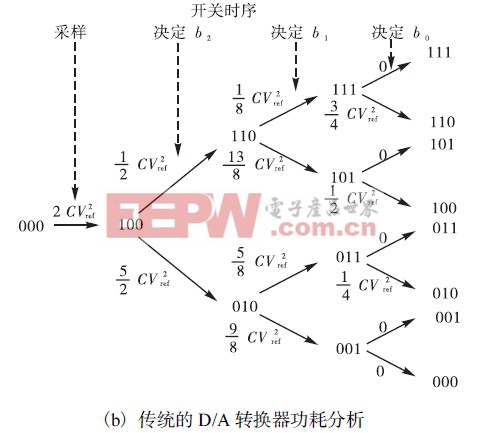

2.3 D/A轉換器的功耗分析

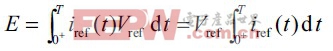

對于電容陣列中的電容,只有當其下極板連接到Vref 時,因充電產生功耗。設電容陣列的建立時間為T,則電容從Vref獲得的能量為:

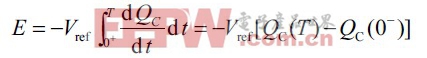

由于電容兩端的電壓不能突變,故QC(0+)=QC(0-),且 iref(t) = -dQC/ dt ,故:

所以,可以計算每一次開關動作時D/A 的功耗。為了減少計算量,仍以3 位D/A 轉換器為例,對兩種D/A 轉換器的功耗進行比較,如圖3 所示,箭頭旁邊的數字為每一次開關動作時消耗的能量。圖3顯示當比較器比較的結果為0 時,采用的結構所消耗的功耗小于傳統的結構。顯然,所設計的D/A 轉換器的平均功耗遠小于傳統的D/A 轉換器。隨著ADC 位數的增加,這種平均功耗的降低效應將會更加顯著。10 位SAR ADC和傳統結構的SAR ADC功耗對比如表1 所示,數據表明改進的SAR ADC 相對于傳統結構下降了21.5%。

圖3 改進的和傳統的D/A功耗分析

評論