一種單端10-bit SAR ADC IP核的設(shè)計(jì)

1.2 DAC電路架構(gòu)

本文采用的DAC架構(gòu)如圖1所示,主要采用分割二進(jìn)制電容加權(quán)結(jié)構(gòu),由逐次逼近邏輯(SAR)產(chǎn)生的控制信號(hào)S0到S11來控制DAC的開關(guān)。其中:

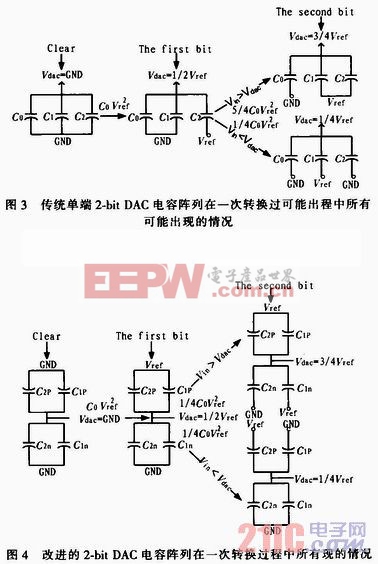

的能量。在進(jìn)行第二位的比較時(shí),DAC進(jìn)行兩種轉(zhuǎn)換:如果Vsh>Vdac,進(jìn)行“up”轉(zhuǎn)換,即C1接Vref(C1起始接GND),因此Vdac=3/4Vref,則需要從參考電壓吸收的能量;相反地,如果VshVdac則需要進(jìn)行“down”轉(zhuǎn)換,如圖4所示;C1接Vref(C1起始接GND)而C2接GND(C2起始接Vref),因此Vdac=1/4Vref,假設(shè)它們?cè)谕粫r(shí)間進(jìn)行變換,則需要的能量。它所需要的能量是“up”轉(zhuǎn)換時(shí)能量的5倍;發(fā)生這種情況是因?yàn)镃2最開始充進(jìn)去的電荷都必須向地(GND)放走,而C1則必須從參考電壓(Vref)上吸收電荷。而分割電容陣列在轉(zhuǎn)換時(shí)的能量消耗較少。為了與上述例子進(jìn)行比較,也拿一個(gè)2-bit的分割電容陣列為例,如圖4所示,其中C1p=C2p=C1n=C2n=C0。清零階段,所有電容全部接GND,沒有能量消耗。當(dāng)清零過后,進(jìn)行第一位的比較時(shí),C1p與C2p的下極板接Vref,DAC的輸出Vdac等于1/2Vref,其中Vref是參考電壓,此時(shí)電容從參考電壓吸收的能量。當(dāng)進(jìn)行第二位的轉(zhuǎn)換時(shí),DAC進(jìn)行兩種轉(zhuǎn)換;如果Vsh>Vdac,進(jìn)行“up”轉(zhuǎn)換,即C1n接Vref(C1n起始接GND),需要從參考電壓吸收的能量;相反的,如果VshVdac,則需要進(jìn)行“down”轉(zhuǎn)換,如圖4所示;C1p接GND(C1p起始接Vref),需要從參考電壓吸收

從上述可以看出,傳統(tǒng)電容陣列在“up”轉(zhuǎn)換時(shí)消耗能量最少,而在“down”轉(zhuǎn)換時(shí)消耗能量最大,而分割電容陣列相對(duì)來說消耗的能量較少。通過仿真可以得知,本文所用的SAR ADC結(jié)構(gòu)由于電容偏轉(zhuǎn)所消耗的平均能量比傳統(tǒng)的SAR ADC要節(jié)省30%左右。

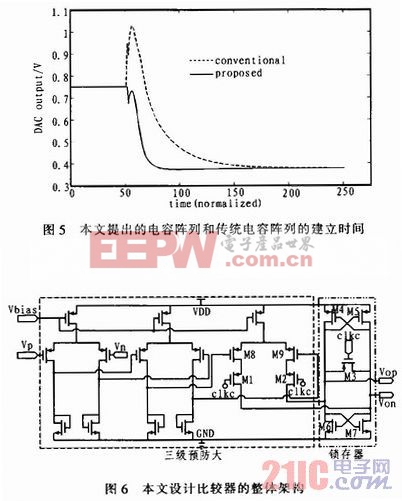

對(duì)于高速應(yīng)用的ADC來說,一個(gè)重要的技術(shù)指標(biāo)就是DAC的建立時(shí)間。在“down”轉(zhuǎn)換過程中,傳統(tǒng)電容陣列中需要有兩個(gè)電容進(jìn)行切換,而控制電容轉(zhuǎn)換的開關(guān)在轉(zhuǎn)換過程中的任何不匹配,無論是隨機(jī)的還是確定的,都可以引起電容陣列向錯(cuò)誤的方向進(jìn)行轉(zhuǎn)換,甚至引起前置放大器的過載。而分割電容陣列在每一位的比較過程中,只有一個(gè)電容變化時(shí),對(duì)開關(guān)信號(hào)的歪斜有很好的抵制作用。圖5是通過仿真對(duì)兩個(gè)電容陣列的建立時(shí)間進(jìn)行了對(duì)比。從仿真結(jié)果可以看出,當(dāng)分割電容陣列和傳統(tǒng)陣列開關(guān)時(shí)間的寬度相同時(shí),分割電容陣列的建立時(shí)間比傳統(tǒng)陣列的建立時(shí)間快了8%左右,而且電容值越大,建立時(shí)間縮小的越明顯。

1.3 比較器電路架構(gòu)

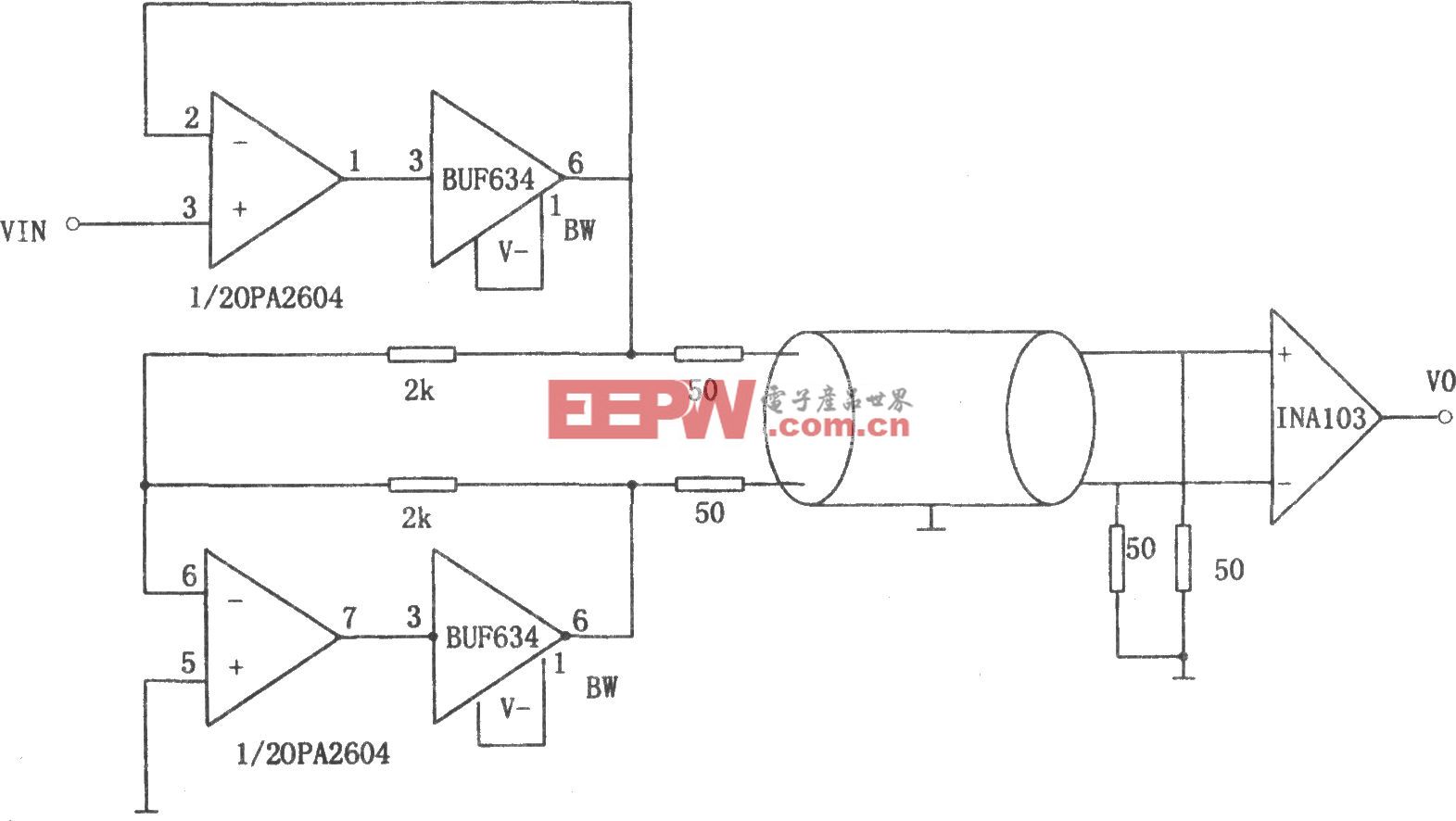

文中采用的比較器結(jié)構(gòu)簡(jiǎn)化如圖6所示,它是由三級(jí)預(yù)放大和鎖存器組成,其中一、二級(jí)預(yù)放大器結(jié)構(gòu)相同。比較器的失調(diào)電壓是影響比較器比較精度的一個(gè)重要參數(shù),進(jìn)而影響整個(gè)ADC的精度,而失調(diào)電壓是經(jīng)過放大器放大之后再存儲(chǔ)在電容上的,所以放大級(jí)的增益不能太大。過大的增益會(huì)使輸出飽和,這樣存儲(chǔ)在電容上的電壓就不能反映真實(shí)的失調(diào)電壓的值,所以三級(jí)預(yù)放大器每一極均有較小的增益,這樣做還可以獲得較大的帶寬,提高比較器整體的響應(yīng)速度。但是比較器的增益過低,則會(huì)影響其精度,而鎖存器的使用則是為了提高比較器的增益,同時(shí)又降低其功耗,進(jìn)而提高比較器的有效精度。

評(píng)論