DSP 在電源設計中的應用

0 引言

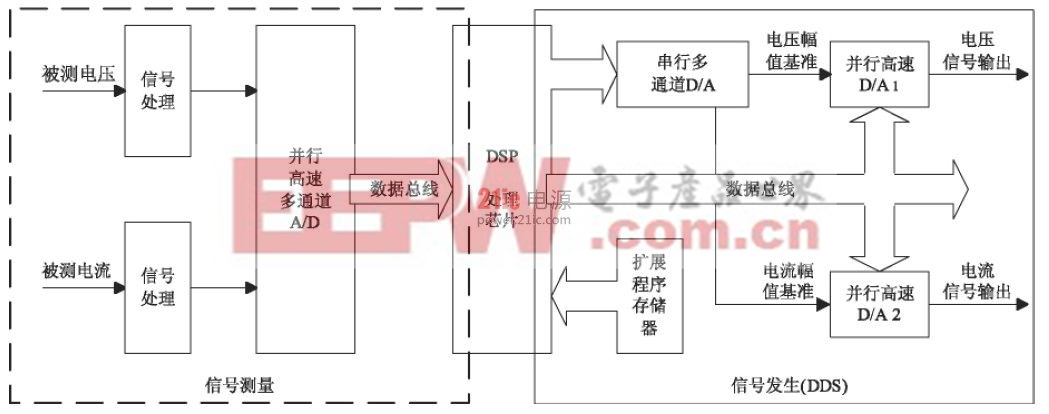

本文引用地址:http://www.104case.com/article/175252.htm電源的信號測控部分由DDS信號發生和信號測量組成。DDS 在電源設計中的應用早已存在。在早期的DDS 設計中,硬件組成由計數器、觸發器等多種多個分立邏輯元件組成; 而在出現可編程邏輯器件CPLD、FPGA 后,DDS 的硬件構成簡化了許多。電源的信號測量,分為頻率、幅值及相位的測量。頻率的測量采用脈沖填充法; 幅值測量則隨著A/D 轉換器的采樣速度及處理器速度的提高,由原來的有較大延遲的真有效值轉換發展為周期實時采樣計算;相位測量則在幅值測量的基礎上,由原來的間相脈沖填充法發展為乘法器矢量測量。

DSP 的高速處理能力,使其可以實現DDS 中的CPLD 或FPGA 及測量電路中的模擬數字混合乘法器的功能,從而使電源的信號發生及測量的硬件設計更簡單。

1 設計方案

方案設計如圖1 所示。DSP 以等時間間隔快速、連續讀取擴展程序存儲器中的波形數據,送入并行高速D/A,并行高速D/A 即可輸出預設信號波形。

輸出信號幅值的調整不如波形數據讀取操作那么頻繁,且對操作完成時間的長短、精度要求也不如波形數據讀取高,所以選擇串行多通道D/A.這樣既可以降低成本,又可以簡化部分硬件設計。以N 個波形讀取時間間隔為計時基礎,DSP 通過并行高速A/D 對經信號處理后的被測信號進行連續采樣,通過計算,可得出被測信號有效值及相位。

2 DDS 的DSP 實現

2.1 DDS 原理

DDS 是利用相位累加原理直接合成所需波形的一種頻率合成技術,典型的DDS 模型由W 位相位累加器、移相加法器、波形存儲器ROM 查找表( LUT) 、D/A 轉換器( DAC) 以及低通濾波器( LPF) 構成。其中相位累加器由W 位加法器與W 位累加寄存器級聯構成。

DDS 工作時,每來一個時鐘脈沖p,加法器將相位步進值Δθ 與累加寄存器輸出的累加相位數據相加,把相加后的結果送至累加寄存器的數據輸入端。

累加寄存器將加法器在上一個時鐘脈沖作用后所產生的新相位數據反饋到加法器的輸入端,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字相加。相位累加器輸出的數據作為查表地址,從波形存儲器( ROM) 中提取對應的波形抽樣值( 二進制編碼) ,送入D/A 轉換器C 中。在相位累加器的數據輸出范圍0 ~ 2W – 1,與波形存儲器中一個完整周期波形的地址,按照特定的函數關系對應起來的前提下,相位累加器的每次溢出,DDS 就相應的輸出了一個周期的波形。因此,相位累加器的溢出頻率就是DDS 輸出的信號頻率。由此可推導出DDS 輸出的信號頻率公式:fout = fclk × Δθ /2W

式中fout為DDS 輸出頻率; fclk為標準時鐘脈沖,固定值; Δθ 為相位步進值,無符號整數,無單位; W 為相位累加器寬度。

從公式( 1) 可以看出,在相位累加器寬度W 為定值、相位步進值Δθ 為1 時,可得出DDS 的最小輸出頻率,即DDS 的頻率分辨率fr.因此,只需要調整相位步進值Δθ,就可以使DDS 的頻率以fr的整數倍輸出。

2. 2 DDS 工作模式選擇

根據公式( 1) 可以看出,在相位累加器寬度W 為定值的前提下,DDS 的輸出頻率,取決于Δθ 和fclk.

Δθ 取值為DDS 的相位分辨率時,DDS 輸出信號的每個周期由固定點數組成,此時fout與fclk成比例關系,DDS 為調頻模式; fclk為定值時,DDS 輸出信號在單位時間內由固定點數組成,此時fout與Δθ 成比例關系,DDS 為調相模式。

調頻模式,其關鍵點為采用鎖相環技術對預置輸出頻率進行倍頻[3 - 4].與調相模式相比,調頻模式不僅要多出鎖相環及相應倍頻邏輯電路的設計,且在進行頻率調整時,信號會有短時間的失鎖,造成輸出信號的振蕩。因此,調相模式是本設計中DDS 的最佳選擇。

2. 3 DSP 實現DDS 的優勢

無論是用分立邏輯器件還是CPLD 或FPGA 設計DDS,其目的都是為了將相位累加器的累加、輸出、波形數據查表等這些運算處理通過硬件電路高速實現。唯一的區別就是應用CPLD 或FPGA 設計DDS,可以將諸多分立器件實現的邏輯電路,通過VHDL 等編程語言編程固化在單一芯片上,從而達到簡化硬件電路設計目的。而采用DSP 設計DDS,則完全可以利用其高速運算能力,通過軟件編程來完成相位累加器的累加、輸出、波形數據查表等運算。因此,相比于采用CPLD 或FPGA,采用DSP設計DDS 更靈活高效。

2. 4 基于DSP 的DDS 的參數設計

2. 4. 1 標準時鐘脈沖fclk

的設計從公式( 1) 可以看出,在相位累加器寬度W 為定值、相位步進值Δθ 為1 時,可得出DDS 的最小輸出頻率,即DDS 的頻率分辨率fr.因此,只需要調整相位步進值Δθ,就可以使DDS 的頻率以fr的整數倍輸出。

P = 2W ÷ Δθ

式中P 為DDS 輸出信號的每個周期的組成點數。

將式( 2) 代入式( 1) ,可得:

fclk = fout × P

在P 足夠多且每點波形數據分辨率與P 匹配的前提下,即可忽略DDS 信號輸出的高頻諧波含量,從而省略硬件設計中的濾波器環節,避免了由濾波器產生的相位偏移。當P = 10000 時,完全可以滿足要求。如設計最大輸出頻率65Hz,可得fclk = 0. 65MHz.

fclk可利用DSP 計數器的中斷產生。考慮到DSP 的工作頻率均為MHz 的整數倍,所以fclk取值1MHz,更加便于中斷的準確產生。

2. 4. 2 相位累加器寬度W 的選取

P = 10000 時,W 取值27 即可滿足設計頻率調節細度≤0. 01Hz 的要求。但相位累加值θ 在DSP 中定義為4 字節的操作數,W 取值27 時,DSP 需對相位累加值進行上限判斷處理后再提取波形數據,從而產生細小的波形畸變并增加一定的運算量。考慮到可利用操作數的自然溢出來減少DSP 的判斷及運算操作,所以W 取值32.

2. 4. 3 周期波形點數P 的選取

在不考慮四舍五入取值的前提下,相位累加器的輸出值與波形數據表數組下標的函數關系如下:

A = P × θ ÷ 2W

式中A 為波形數據數組下標; P 為波形數據點數; θ為相位累加器輸出值。

由于DSP 中沒有現成的除法指令,除法是靠被除數與除數之間的移位相減來實現的,采用該函數的算法將增加DSP 的運算量。因此,可以通過事先將P ÷ 2W 作為系數,減少求數組下標運算步驟。但P ÷ 2W 可能為小數,如果取整計算,將使下標出現跳躍性變化,導致輸出波形畸變增大。不取整計算時,如使用定點DSP,雖然價格便宜且運算速度較快,但會增加系統運算量。而使用浮點DSP,運算速度較慢且硬件費用會有相對提高。考慮到DSP 要進行多線程的任務工作,需要較快的運算速度,因此選用定點DSP,并對波形數據數組下標的算法進行進一步的改進。

將公式( 4) 中P 的點數由相位調節細度要求的最低點數Pmin調整至大于Pmin的最小的2 的X 次冪。

將P 代入公式( 4) ,簡化得:

A = θ /2W-X

在DSP 中,所有的值都用二進制來表示。所以,在公式( 5) 里所有變量的取值均為無符號整數的前提下,A 的獲得就簡化成了對θ 進行( W – X) 次的右移。

評論