一種CPLD自供電系統實現

有一種常見的工業和消費應用,即按一個長間隔(如每分鐘一次)對環境條件,如GPS(全球定位系統)位置、電壓、溫度或光線進行采樣的系統。這類系統正越來越多地采用無線和電池供電方式,它每分鐘蘇醒過來,作一次采樣,將數據傳輸到一個中央數據采集終端,然后再次進入睡眠狀態。本設計實例用一片Altera EPM240-T100 CPLD(復雜可編程邏輯器件)中的一小部分,結合一些分立電容、電阻、二極管和MOSFET,通過一個RC定時器電路,自動將一個CPLD系統從完全斷電狀態喚醒。

本文引用地址:http://www.104case.com/article/174970.htm

CPLD(Complex Programmable Logic Device)復雜可編程邏輯器件,是從PAL和GAL器件發展出來的器件,相對而言規模大,結構復雜,屬于大規模集成電路范圍。是一種用戶根據各自需要而自行構造邏輯功能的數字集成電路。其基本設計方法是借助集成開發軟件平臺,用原理圖、硬件描述語言等方法,生成相應的目標文件,通過下載電纜(在系統編程)將代碼傳送到目標芯片中,實現設計的數字系統。CPLD主要是由可編程邏輯宏單元(MC,Macro Cell)圍繞中心的可編程互連矩陣單元組成。其中MC結構較復雜,并具有復雜的I/O單元互連結構,可由用戶根據需要生成特定的電路結構,完成一定的功能。由于CPLD內部采用固定長度的金屬線進行各邏輯塊的互連,所以設計的邏輯電路具有時間可預測性,避免了分段式互連結構時序不完全預測的缺點。

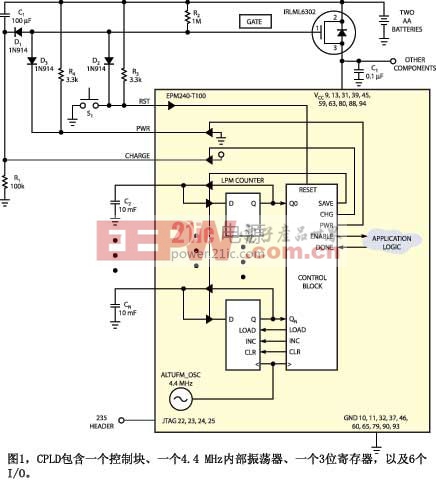

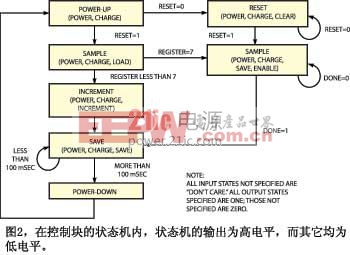

圖1是基本的CPLD開/關定時器。Q1是一片IRLML6302 P溝道MOSFET,用作系統的電源控制開關。當門節點為VCC時,R2上拉,連接CPLD和整個系統的電源均被切斷,只有RC電路消耗少量電能。CPLD帶有一個控制塊、一個4.4MHz內部振蕩器、一個3位寄存器,以及6個I/O.圖2為控制部分的狀態機。從掉電到上電的虛線表示時間延遲,該時間延遲在系統斷電時由R1與C1構成的RC電路測量。開關S1接通時電路初始化。當S1閉合時,D2將門節點拉低,當門電壓低于VCC 0.7V時Q1導通。Q1加電不到200ms后,EPM240-T100工作在上電狀態。上電狀態將電源節點拉低,將門電壓保持在0.7V,在開關打開后使Q1維持導通。

接下來,采樣與傳輸電路開始工作,使done信號為0.當采樣與傳輸完成時,done信號變為1,而控制塊進入保存狀態。保存狀態按照Register 1中的值,將電容C2充電至CN.保存狀態激活100ms時間,使輸出對10mF電容完全充電。經過100ms后,控制塊進入斷電狀態,停止驅動充電節點與電源節點。R4將電源節點拉高,而R2拉高門節點。

當門節點使VCC-VTQ1達到大約 2.3V時,Q1切斷系統的供電。EPM240-T100的所有I/O均處于高阻抗狀態,并且不影響門節點或充電節點。充電節點開始于VCC,并在電源關斷時開始通過R1放電。一旦充電節點掉落到2.3V,D1拉低門節點。當充電節點達到1.6V 時,門節點為2.3V,Q1 導通。

器件在上電狀態上電,但很快轉至采樣狀態。采樣狀態記錄電容C2、C3和C4上的值。這些電容用作非易失存儲器,保存以前上電循環的次數。如果C4 ~ C2上采樣的Register 1值小于7,則控制塊開始遞增,而Register 1的值以1為增量增加。然后,控制塊再次進入保存狀態,C2 ~C4充電到一個新的二進制值001.器件再次斷電。在第8次上電循環,或上電后大約80s,控制塊轉為使能狀態,因而開始一個新的采樣與傳輸順序。這個過程每80s重復一次。你可以調整C1和R1改變Register1的大小和使能循環之間的計數,就可以改變這個80s的周期。由于80s周期包含8個較小的上電采樣、測試與斷電循環,供電的占空周期小于3%,因此,這種方案將電池壽命增加了33倍。

評論