TMS320F240片內(nèi)PWM實(shí)現(xiàn)D/A擴(kuò)展功能

關(guān)鍵詞:數(shù)字信號處理器 TMS320F240 PWM D/A轉(zhuǎn)換

TMS320F240(簡稱F240) 作為一種高速、高集成度、低成本的微控制器,功能非常強(qiáng)大。美中不足的是,F(xiàn)240芯片本身雖然集成了眾多滿足數(shù)字控制系統(tǒng)所需的先進(jìn)外圍設(shè)備,包括A/D轉(zhuǎn)換等功能,卻唯獨(dú)沒有集成D/A轉(zhuǎn)換功能,因此,在TMS320F240芯片的實(shí)際應(yīng)用過程中,為其增加 D/A轉(zhuǎn)換接口是很有必要的。

本文提出的基于F240芯片PWM輸出的D/A轉(zhuǎn)換擴(kuò)展功能設(shè)計(jì),是一種對F240片內(nèi)的D/A轉(zhuǎn)換設(shè)計(jì)。通過F240片內(nèi)的PWM輸出,再加上簡單的外圍電路及對應(yīng)的軟件設(shè)計(jì),實(shí)現(xiàn)對PWM的信號處理,得到穩(wěn)定、精確的模擬量輸出。

1 原理及誤差分析

1.1 基本原理

F240芯片提供的PWM輸出,是一種周期和占空比均可變、幅值為5 V的脈寬調(diào)制信號。實(shí)現(xiàn)PWM信號到D/A轉(zhuǎn)換輸出的理想方法是:采用模擬低通濾波器濾掉PWM輸出的高頻部分,保留低頻的直流分量,即可得到對應(yīng)的D/A輸出,如(圖1)所示。低通濾波器的帶寬決定了D/A輸出的帶寬范圍。

為了對PWM信號的頻譜進(jìn)行分析,以下提供了一個(gè)設(shè)計(jì)濾波器的理論基礎(chǔ)。傅里葉變換理論告訴我們,任何一個(gè)周期為T的連續(xù)信號f(t),都可以表達(dá)為頻率是基頻的整數(shù)倍的正、余弦諧波分量之和。它是以時(shí)間軸原點(diǎn)為對稱點(diǎn)的、單極性的PWM信號,表達(dá)式為

其中,f=1/T為基頻,式中An、 Bn為各自獨(dú)立的傅里葉系數(shù):

由于f(t)是一個(gè)關(guān)于原點(diǎn)對稱的偶函數(shù),因此Bn項(xiàng)為0,只需計(jì)算An項(xiàng)即可。只要扣除直流分量A0,由f(t)=-f(t+T/2),An的偶系數(shù)也將為0,因此,對占空比為k、幅值為5 V的PWM信號有:

A0=5k

Bn=0

由式(5)可知,直流分量A0就是所需要的 D/A輸出,只要改變PWM信號的占空比k,就能得到電壓范圍為0~5 V的D/A轉(zhuǎn)換輸出;An代表PWM信號的高頻直流分量,頻率為PWM信號基頻的整數(shù)倍。因此,對于基頻為10 kHz的PWM信號,一個(gè)理想的剪切頻率≤10 kHz的濾波器即可完全濾掉PWM信號的高頻諧波分量An,得到低頻的直流分量A0,從而實(shí)現(xiàn)PWM信號到D/A輸出的轉(zhuǎn)換。

1.2 誤差分析

D/A轉(zhuǎn)換輸出的電壓信號有一個(gè)紋波疊加在直流分量上。這是D/A轉(zhuǎn)換誤差的來源之一。影響D/A轉(zhuǎn)換誤差的另外一個(gè)重要因素,取決于PWM信號的基頻。對于時(shí)鐘頻率為20 MHz的F240芯片,產(chǎn)生一個(gè)20 kHz的PWM信號,意味著每產(chǎn)生一個(gè)周期的PWM信號,要計(jì)數(shù)1000個(gè)時(shí)鐘。即所得的直流分量的最小輸出為1個(gè)時(shí)鐘產(chǎn)生的PWM信號,等于5 mV(5 V1/1000),剛好小于10位的D/A轉(zhuǎn)換器的最小輸出4.8 mV(5 V/1024)。因此,理想情況下,PWM信號的頻率越低,所得的直流分量就越小,D/A轉(zhuǎn)換的分辨率也就相應(yīng)的越高。如果將PWM信號的頻率從20 kHz降到10 kHz,則直流分量輸出的最小輸出為2.5 mV(5 V/2000),接近于11位的分辨率。但是,隨著PWM信號基頻的減小,諧波分量的頻率也隨之降低,就會(huì)有更多的諧波通過相同帶寬的低通濾波器,造成輸出的直流分量的紋波更大,導(dǎo)致D/A轉(zhuǎn)換的分辨率降低。所以,單純降低PWM信號的頻率不能獲得較高的分辨率。通過以上分析可知,基于DSP芯片PWM輸出的D/A轉(zhuǎn)換輸出的誤差,取決于通過低通濾波器的高頻分量所產(chǎn)生的紋波和由PWM信號的頻率決定的最小輸出電壓這兩個(gè)方面。所以要獲得最佳的D/A分辨率,在選取PWM信號的頻率時(shí)不能太小,要適當(dāng)?shù)卣壑裕x取一個(gè)最合適的值。如表1所列,通過Matlab仿真,可以得到最佳D/A分辨率下的PWM信號頻率。

表1 不同設(shè)計(jì)參數(shù)下F240芯片PWM輸出實(shí)現(xiàn)D/A轉(zhuǎn)換的分辨率

| 低通濾波器階數(shù) | 傳遞函數(shù) | -3dB帶寬/Hz | PWM頻率f/kHz | 紋波Vpp/V | PWM頻率決定的分辨率 | D/A轉(zhuǎn)換的分辨率/位 |

| 一階 | 1/(RCs+1) | 1000 | 10 | 0.78 | 2.5 | 2.7 |

| 20 | 0.39 | 5.0 | 3.7 | |||

| 二階 | ω2n/(s2+2ξωns+ω2n) | 1000 | 10 | 0.062 | 2.5 | 6.3 |

| 20 | 0.016 | 5.0 | 7.9 | |||

| 三階 | 1/(a3s3+a2s2+a1s+a0) | 1000 | 10 | 0.0064 | 2.5 | 9.1 |

| 20 | 0.00081 | 5.0 | 9.7 |

2 硬件設(shè)計(jì)

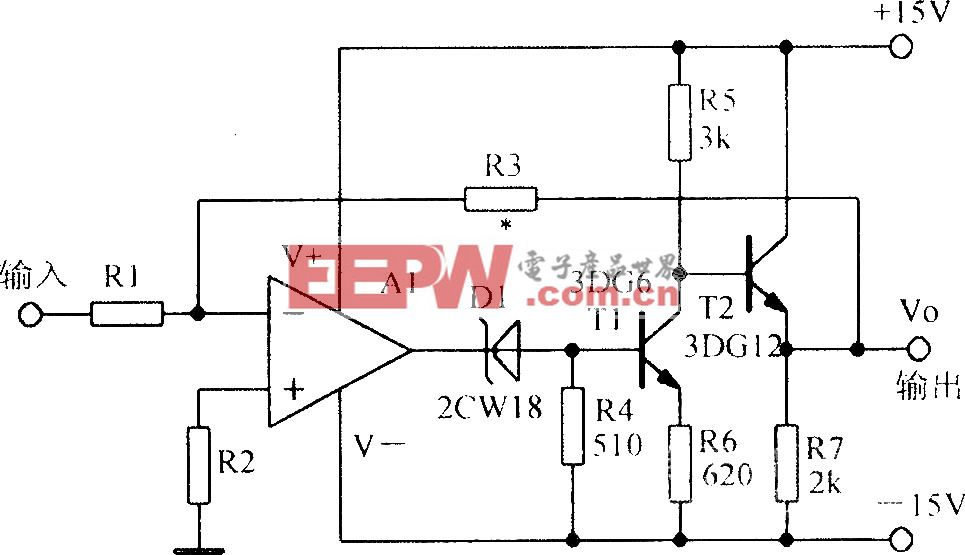

一般來說,F(xiàn)240的PWM輸出要通過具有一階阻容濾波及光電隔離功能的I/O接口板后,方可與實(shí)際控制對象連接。為了獲得高精度的D/A輸出,在濾波之前應(yīng)先通過緩沖器,整體設(shè)計(jì)框圖如圖2所示。

濾波器的運(yùn)算放大器選用OP07。它溫漂小、阻抗低、吸收電流大、精度高。考慮到實(shí)際情況,設(shè)計(jì)模擬低通濾波器的階數(shù)一般不超過三階,否則會(huì)增大系統(tǒng)的復(fù)雜性,增加系統(tǒng)的成本。下面主要介紹有源低通濾波器的參數(shù)設(shè)計(jì)。

2.1 二階Butterworth低通濾波器

圖3(a)所示,是二階Butterworth低通濾波器(最平幅值濾波器)的一種實(shí)現(xiàn)電路,其傳遞函數(shù)為

在-3 dB帶寬為1000 kHz的條件下:

A0=1

由于考慮到不可能找到與所計(jì)算的R、C值完全一致的電阻、電容值,而只能選取與實(shí)際的電阻、電容值最接近的值,故求解得到:

C1 = 0.1 μF, C2=0.01 μF,

R1=22 kΩ, R2=1 kΩ (7)

在這些參數(shù)下,實(shí)際的帶寬是1074 Hz,Q值為0.645,與理想的二階Butterworth低通濾波器有一定的誤差。

2.2 三階低通濾波器

圖3(b)所示為三階低通濾波器的一種實(shí)現(xiàn)電路,其傳遞函數(shù)為

Vo/Vi=1/(a3s3+a2s2+a1s+a0) (8)

其中, a0=1+R1/R4

a1=R1(C1+C2)+(R2+R3)C2+R1C2(R2+R3)/R4

a2=R3C2C3(R1+R2)+R2R3C2C3+R1R2R3C2C3/R4

a3=R1R2R3C1C2C3

在-3 dB帶寬為1000 kHz的條件下,求解得到:

R1=1.6 kΩ,R2=2.4 kΩ,R3=7.5 kΩ,R4=∞,C1=0.1μF,C2=0.01μF,C3=0.047μF (9)

R4決定濾波器直流分量的增益,選取R4=∞(即不安裝R4),則D/A輸出增益為1;要想改變帶寬大小,只須保持R4和電容值不變,改變其它電阻的阻值即可。

圖3 低通濾波器電路

3 軟件程序設(shè)計(jì)和實(shí)驗(yàn)結(jié)果

利用TMS320F240配套的EVM(Evaluation Module)板作為DSP的實(shí)驗(yàn)平臺(tái),給定一模擬電壓作為F240的A/D輸入,將A/D轉(zhuǎn)換的值作為產(chǎn)生PWM波形的DSP定時(shí)器中比較寄存器的值;通過中斷,不斷獲取最新的A/D轉(zhuǎn)換值,改變PWM波形的占空比,得到對應(yīng)幅值的PWM波形,再將所得的20 kHz的PWM信號輸入給濾波器,用數(shù)字示波器觀察濾波器的D/A輸出,以評價(jià)這種D/A轉(zhuǎn)換方法的實(shí)際效果。

3.1 通過D/A轉(zhuǎn)換產(chǎn)生對應(yīng)幅值PWM波形的DSP程序

基于DSP功能模塊化的特點(diǎn),其匯編程序的編制主要分三個(gè)步驟:① 初始化設(shè)置時(shí)鐘源模塊,得到所需的CPUCLK和SYSCLK; ② 設(shè)置事件管理模塊,初始化定時(shí)器和A/D轉(zhuǎn)換操作; ③ 編寫定時(shí)中斷服務(wù)子程序,即可完成從A/D轉(zhuǎn)換產(chǎn)生對應(yīng)幅值的PWM波形輸出。部分程序代碼如下:

;設(shè)置 PLL模塊

LDP #224;

SPLK #0000000001000001b,CKCR0

;SYSCLK=CPUCLK/2

SPLK #0000000010111011b,CKCR1

;CLKIN(OSC)=10MHz, CPUCLK=20MHz

SPLK #0000000011000011b,CKCR0

;使能鎖相環(huán)(PLL)操作

SPLK #0100000011000000b,SYSCR

;CLKOUT=CPUCLK

;設(shè)置EV 管理器

LDP #232;

SPLK #0,T1CMPR ;初始化定時(shí)比較寄存器

SPLK #0000000001010101b,GPTCON

;通用定時(shí)器的PWM輸出為低有效

SPLK #1000,T1PR ;設(shè)置PWM波形的周期為20 kHz

SPLK #0000h,T1CNT ;初始化計(jì)數(shù)寄存器

SPLK #0001000000001010b,T1CON

;設(shè)置連續(xù)增計(jì)數(shù)方式,使能比較操作

SPLK #0000000010000000b,EVIMRA

;清除定時(shí)器1比較中斷屏蔽位

LDP #224

SPLK #1000110100000010b,ADCTRL1

;設(shè)置A/D連續(xù)轉(zhuǎn)換模式,選擇通道CH0

SPLK #0000000000000101b,ADCTRL2

;設(shè)置A/D轉(zhuǎn)換輸入時(shí)鐘預(yù)定標(biāo)因子為16

LDP #232

SBIT1 T1CON,B6_MSK ;使能定時(shí)器1中斷啟動(dòng)位

LDP #224

SBIT1 ADCTRL1,B0_MSK;使能A/D轉(zhuǎn)換啟動(dòng)位

CLRC INTM;

END B END ;等待定時(shí)器1中斷的產(chǎn)生

;產(chǎn)生PWM 波形ISR

Change_CMPR:

LDP #224 ;定時(shí)器1比較中斷服務(wù)子程序

LACC ADCTRL1;

SACL ADCTRL1 ;清除片內(nèi)A/D轉(zhuǎn)換中斷標(biāo)志位

LACC ADCFIFO1;讀取最新的A/D轉(zhuǎn)換值

RPT #5;

SFR ;把存于結(jié)果寄存器的高10位的A/D

;轉(zhuǎn)換值移至ACC的低十位

LDP #232;

SACL T1CMPR ;將A/D轉(zhuǎn)換值存于定時(shí)比較寄存器

LACC EVIFRA;

SACL EVIFRA ; 清除定時(shí)器中斷標(biāo)志

CLRC INTM ;開中斷

RET ;中斷返回

3.2 PWM輸出實(shí)現(xiàn)D/A轉(zhuǎn)換功能的實(shí)驗(yàn)結(jié)果

如圖4所示,是在給定一恒定的3.5 V模擬電壓作為F240的A/D輸入的情況下,所得的PWM輸出實(shí)現(xiàn)D/A轉(zhuǎn)換的波形圖。

波形1為不通過低通濾波器的原始PWM信號。

波形2為PWM信號通過一階低通模擬低通濾波器后的D/A輸出波形,濾波器參數(shù)為R=1 kΩ,C=0.1μF,帶寬為1592 Hz。可以看出,一階下的D/A輸出為一鋸齒波,可用性很差。

波形3為PWM信號通過二階Butterworth低通模擬濾波器后的D/A輸出波形,濾波器參數(shù)按照式(7)選取。可以看出,二階下的D/A輸出平均值接近3.5 V,只是尖峰毛刺比較大,有一定的可用性。

波形4為PWM信號通過三階低通模擬濾波器后的D/A輸出波形,濾波器參數(shù)按照式(9)選取。可以看出,三階下的D/A輸出毛刺很小,D/A轉(zhuǎn)換的分辨率約為9.2位, 非常接近于理想的D/A輸出,可用性強(qiáng)。

實(shí)驗(yàn)結(jié)果表明,DSP的PWM信號經(jīng)過三階低通模擬濾波器后,得到的D/A轉(zhuǎn)換輸出帶寬較大,在1000 Hz左右;分辨率較高,約為9.5位,可以滿足實(shí)際應(yīng)用的需要。

pwm相關(guān)文章:pwm原理

評論