基于AVR單片機與FPGA的低頻數字式相位測量儀

3 系統硬件電路的設計

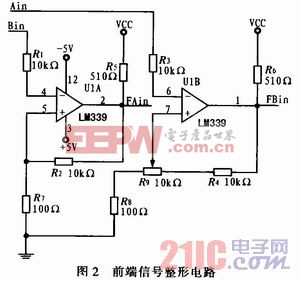

3.1 前端信號調理電路的設計

施密特觸發器(遲滯比較器)雖然可以很好地消除比較器過零引起的抖動,但是其輸出信號和輸入信號存在相位差,如果兩路被測信號的幅度基本相等且兩個施密特觸發器的門限電平又很接近,則施密特觸發器引入的相位誤差對測量系統誤差幾乎無影響。

采用LM339內部有4個獨立的電壓比較器,該電壓比較器的特點是:失調電壓小,典型值為2 mV;電源電壓范圍寬,雙電源電壓為±1~±18 V;對比較信號源的內阻限制較寬。同相和反相輸入端電壓差別大于10 mV就能確保輸出能從一種狀態可靠地轉換到另一種狀態,輸出端相當于一只不接集電極電阻的晶體三極管,在使用時輸出端到正電源一般須接一只電阻。在跳變電壓值附近的干擾不超過回差AU,輸出電壓的值就將是穩定的。正反饋可以加快比較器的響應速度。由于遲滯比較器加的正反饋很強,遠比電路中的寄生耦合強得多,所以可免除由于電路寄生耦合而產生的自激振蕩。通過調節電位器,使兩個施密特觸發器的門限電平基本相等,保證輸入電路對相位差測量不帶來誤差。電路如圖2所示。本文引用地址:http://www.104case.com/article/172687.htm

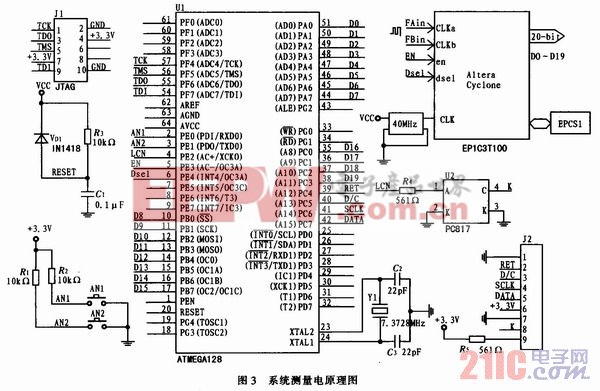

3.2 系統測量電路設計

以單片機為核心設計相位儀,如其晶振為24 MHz,單片機C/T的計數誤差為1個機器周期為±0.5 μs,則絕對誤差為360°x0.5 μs/50μs=3.6°,所以,當被測信號頻率很高時很難滿足測量要求。

本設計采用AVR單片機與FPGA相結合的方案,FPGA實現數據采集,將所測信號的頻率和相位差所對應時間差轉換為二進制數據傳給單片機;單片機從FPGA獲取數據,經過運算、轉換等數據處理,將被測信號的頻率和相位差在LCD上顯示。

系統電原理圖如圖3所示。MCU采用ATMEL公司的AVR單片機ATmega128,具有先進的RISC結構,大多數指令在一個時鐘周期內完成,有32個8位通用工作寄存器及外設控制寄存器,克服了一般單片機單一累加器數據處理帶來的瓶頸。有128 KB的系統內可編程Flash,4 KB的EEPROM以及4 KB的內部SRAM,遵循JTAG標準的邊界掃描功能,支持擴展的片內調試,可通過JTAG接口實現對Flash、EEPROM、熔絲位和鎖定位的編程。

FPGA采用Altem Cyclone系列的EP1C3T100,配置芯片為EPCS1,VHDL功能程序經過全編譯會生成.sof和.pof文件,配置的下載為Byte-Blaster II,[Mode]項選擇“JTAG”為把.sof文件配置到FPGA芯片EP1C3T100中,用于調試;[Mode]項選擇“Active Serial Programming”為把.pof文件下載到配置芯片EPCS1中,系統重新上電時正常運行。

LCD采用HTM12864,為128x64串行數據傳送液晶顯示器,背光燈通過光耦受到控制。

ATmega128和EP1C3T100設計各自的JTAG接口。圖3繪出了ATmega128和EP1C3T100的接口D0~D19、EN、Dsel、LCN;ATmega128與HTM12864的接口RET、D/C、SCLK、DATA;EP1C3T100的輸入信號FAin和FBin,66 MHz外部有源晶振,配置芯片EPCS1。

評論