AVR AT90S1200 IP核設(shè)計(jì)及復(fù)用技術(shù)

4 FSPLC微處理器核SOC設(shè)計(jì)

4.1 SOC硬件結(jié)構(gòu)

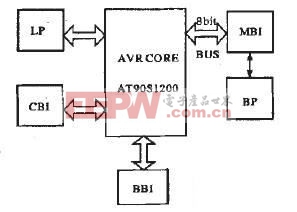

根據(jù)FSPLCSOC系統(tǒng)功能定義,設(shè)計(jì)完成FSPLC微處理器硬件結(jié)構(gòu),如圖4所示。

圖4 FSPLCSOC硬件結(jié)構(gòu)框圖

FSPLCSOC由AT90S1200、布爾處理器BP、存儲(chǔ)器位接口MBI、邏輯處理器LP,CAN總線1。0接口CBI、底板總線接口BBI等6個(gè)模塊組成。AT90S1200模塊是SOC的核心,實(shí)現(xiàn)PLC指令的執(zhí)行;BP模塊由兩個(gè)位累加器和一個(gè)位邏輯堆淺BLS組成,該結(jié)構(gòu)可以有效處理IEC61131-3(國(guó)際電工委員會(huì)制訂的基于Windows編程語(yǔ)言標(biāo)準(zhǔn))PLC指令表語(yǔ)句中復(fù)雜的嵌套邏輯運(yùn)算,使運(yùn)行頻率最高的位指令達(dá)到最大的執(zhí)行速度;存儲(chǔ)器位接口模塊由一個(gè)存儲(chǔ)器位尋址接口邏輯和一個(gè)8選1選擇器組成,為布爾處理器和數(shù)據(jù)存儲(chǔ)器之間的位訪間接口;CAN總線1。0接口CBI模塊和外部基于Atmega8515的USB-CAN適配器相連,通過(guò)此適配器FSPLC可以和其他帶有CAN接口的PLC實(shí)現(xiàn)CAN通訊;通過(guò)底板總線接口BBI模塊可以在FSPLC片外擴(kuò)展模塊,最多可以達(dá)到8個(gè),包括I/0擴(kuò)展模塊、AID模塊、D/A模塊、計(jì)數(shù)模塊等。其中AT90S1200,MBI,LP,CBI,BBI模塊通過(guò)內(nèi)部總線連接,BP通過(guò)MBI模塊轉(zhuǎn)換實(shí)現(xiàn)和其他模塊的連接。

4.2 FSPLCSOC仿真、綜合、驗(yàn)證

由于SOC設(shè)計(jì)是一種面向IP核集成的設(shè)計(jì),整合后的SOC模塊同第三方IP核復(fù)用一樣需要進(jìn)行模塊的仿真、綜合和驗(yàn)證。FSPLC SOC同復(fù)用AT90SI200核一樣借助ModelSim進(jìn)行功能仿真和驗(yàn)證后時(shí)序仿真,借助Synplify Pro進(jìn)行綜合。

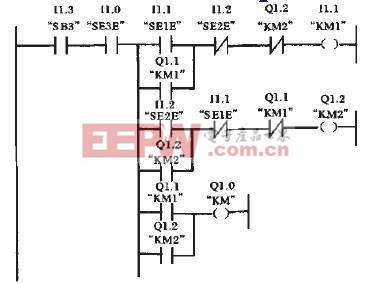

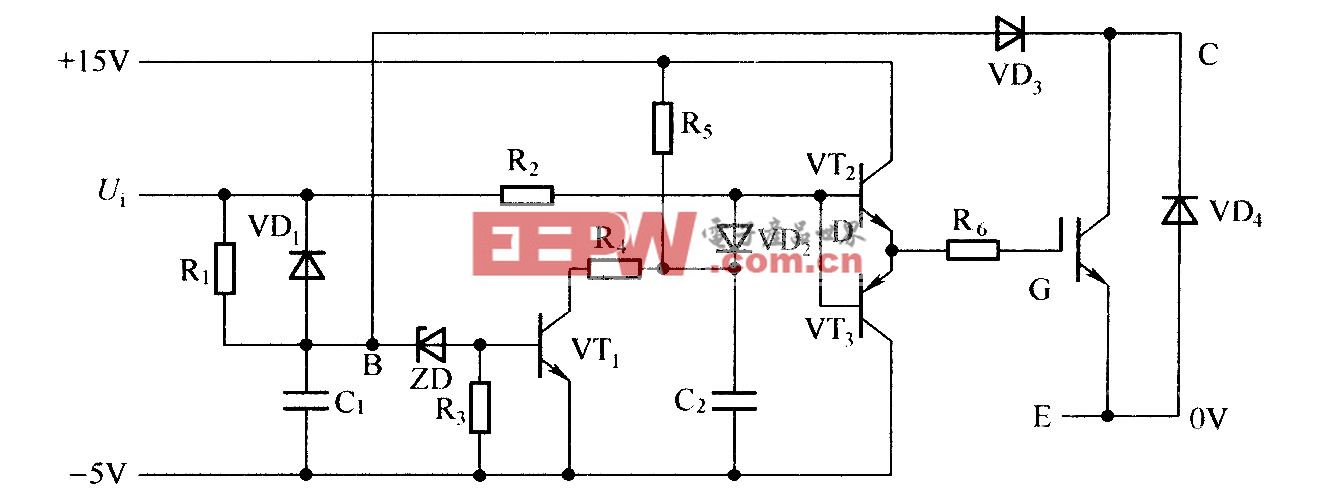

下面具體描述FSPLCSOC的驗(yàn)證,SOC設(shè)計(jì)中包含了系統(tǒng)設(shè)計(jì)和模塊設(shè)計(jì),因此SOC驗(yàn)證一般包含了模塊驗(yàn)證、芯片驗(yàn)證和系統(tǒng)驗(yàn)證三個(gè)部分。由于FSPLCSOC涉及到的主要是數(shù)字IP核,文中采用Altera NioslI開(kāi)發(fā)板作為設(shè)計(jì)的驗(yàn)證平臺(tái),該開(kāi)發(fā)板帶有一個(gè)20多萬(wàn)門(mén)的Altera EP20K200EFC484-2的FPGA芯片、撥碼開(kāi)關(guān)、數(shù)碼顯示器等,用一個(gè)實(shí)際PLC應(yīng)用程序在此開(kāi)發(fā)板上對(duì)FSPLCSOC進(jìn)行了可行性驗(yàn)證,同時(shí)通過(guò)對(duì)AVR編譯器Avral。0的編譯代碼變量中增加PLC指令代碼,使之能夠?qū)L(:指令進(jìn)行編譯。圖5,圖6分別為PLC控制程序的梯形圖及其匯編程序。

圖5 PLC控制程序的梯形圖

開(kāi)發(fā)板的撥碼開(kāi)關(guān)SWl的1、2、3、4來(lái)模擬上述開(kāi)關(guān)的閉合,觀察數(shù)碼顯示器Dl數(shù)碼段明暗,驗(yàn)證設(shè)計(jì)的可行性。FSPLCSOC在Altera Nios開(kāi)發(fā)板的FPGA芯片上進(jìn)行了可行性驗(yàn)證,獲得了理想的運(yùn)行效果:在33MHz晶振下,執(zhí)行基本邏輯指令速度為0。09μ/條,達(dá)到了國(guó)際上大中型PLC的處理速度。

圖6 PSPLC匯編程序

5 結(jié)束語(yǔ)

目前IC產(chǎn)業(yè)中,SOC已成為最主要的集成電路設(shè)計(jì)方法8位RISC微處理器芯片設(shè)計(jì)正在向SOC化發(fā)展,通過(guò)IP核復(fù)用方法以縮短周期、降低成本、提高效率。文中基于IP核復(fù)用和SOC技術(shù)借助ModelSim、Synplify Pro、QuartusⅡ等EDA軟件設(shè)計(jì)了擁有自主知識(shí)產(chǎn)權(quán)的專(zhuān)用PLC微處理器SOC模塊FSPLC,在復(fù)用了第三方AVRAT90SI200IP核基礎(chǔ)上集成了自行設(shè)計(jì)的LP、BP、MBI、CBI、BBI等模塊,具有快速處理PLC梯形圖程序、快速處理IL語(yǔ)句表中復(fù)雜的嵌套邏輯運(yùn)算、PLC之間CAN總線通訊等優(yōu)點(diǎn)。最后采用Altera NiosII作為驗(yàn)證平臺(tái),對(duì)實(shí)際的PLC應(yīng)用程序做了可行性驗(yàn)證,獲得了理想的效果。

評(píng)論