基于Q-Coder算術編碼器的IP核設計與仿真

4 實驗結果與分析

本文引用地址:http://www.104case.com/article/170822.htm

(1)將Verilog源程序在QuartusⅡ軟件中綜合后,得到的參數如下:

1)器件名稱:EP20K200efc484-2x;

2)FPGA時鐘最高頻率:45.18MHz;

3)Total logic elements:3660/8320 (44%)。

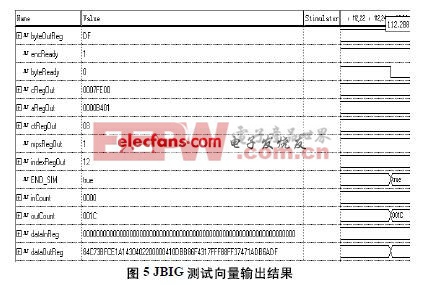

(2)功能驗證。目前,只有JBIG[8]標準中有驗證算術編碼器編碼正確性的測試向量,因此該測試向量被用以測試本文設計IP核的正確性。需要說明的是:JBIG標準中的算術編碼器會產生“FF AC”標志位[8],而JPEG2000中的MQ-Coder算術編碼器并不產生該標志位[1]。

將JBIG中的測試向量作為輸入,經過本文設計的算術編碼IP核處理后的結果如圖5所示,由圖5可知本文設計的算術編碼IP核完全正確。

(3)由概述可知,Jasper軟件具有一定的權威性,因此在實驗中被使用。表1列出了對于同一個圖像文件,Jasper軟件中算術編碼模塊執行所需的時間和本文設計的算術編碼IP核執行所需的時間以及兩者時間之比。

5 結論

本文提出的一種實現算術編碼的集成電路IP核,經過仿真和FPGA驗證,能夠符合JPEG2000標準,仿真結果表明,在相同的條件下,該IP核編碼所需時間僅約為軟件編碼所需時間的40%,從而大大提高了算術編碼的效率,使得將來其應用于實時處理系統成為可能;并且將來可以定制所需的ASIC電路,用于新一代數字照相機等具有廣泛市場前景的項目。

評論