LVDS技術(shù)在某成像光電跟蹤產(chǎn)品中的應(yīng)用

2 LVDS在某成像光電跟蹤產(chǎn)品中的應(yīng)用

2.1 系統(tǒng)應(yīng)用簡介

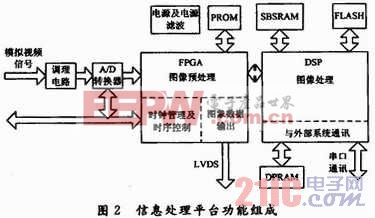

某成像光電跟蹤產(chǎn)品信息處理平臺(tái)采用FPGA+DSP的設(shè)計(jì)框架,結(jié)構(gòu)框圖如圖2所示。本文引用地址:http://www.104case.com/article/168902.htm

該信息處理平臺(tái)在FPGA和DSP外圍增加調(diào)理電路、A/D裝換器、PROM、SBSRAM、DPRAM、FLASH、電源及電源濾波電路等。FPGA+DSP架構(gòu)最大的特點(diǎn)是結(jié)構(gòu)靈活,適于模塊化設(shè)計(jì),能有效地提高算法效率,因而非常適用于成像系統(tǒng)的信息處理。從圖2可以看出,該系統(tǒng)通過FPGA,利用LVDS標(biāo)準(zhǔn)電路設(shè)計(jì)完成圖像數(shù)據(jù)的輸出。在該系統(tǒng)中,LVDS有三路差分輸出,其中兩路傳送數(shù)據(jù)(DA,DB),一路傳送時(shí)鐘(C)。傳送格式的要求如下:DA(DAX)為發(fā)送16位數(shù)據(jù)線,傳送系統(tǒng)給圖像采集設(shè)備的所有數(shù)據(jù)。包括每幀開頭發(fā)送一個(gè)幀計(jì)數(shù),幀正程發(fā)送圖像數(shù)據(jù)(實(shí)時(shí)圖像數(shù)據(jù)、濾波圖像數(shù)據(jù)及二值像數(shù)據(jù),按DSP要求傳送)。圖像數(shù)據(jù)為12位或14位,按需要傳送。16位數(shù)據(jù)的分配如下:最高位為奇偶校驗(yàn)位,“1”表示奇數(shù),“0”表示偶數(shù);次高位為正逆掃信號(hào),“1”表示正掃,“0”表示逆掃;在每幀的開頭,圖像數(shù)據(jù)輸出之前,添加2個(gè)驗(yàn)證字——FDB18540,作為接收方判斷每幀數(shù)據(jù)傳送的起始點(diǎn);幀正程開始后,傳圖像數(shù)據(jù)14位,如傳的是12位圖像數(shù),則其14,13位填0,后12位為圖像數(shù)據(jù)。

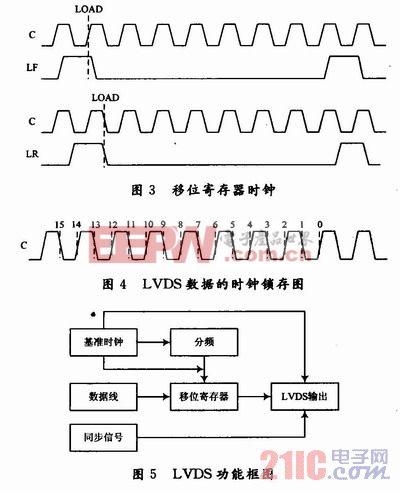

DB(DBX):發(fā)送同步信號(hào),每字同步,與首數(shù)據(jù)最高位同時(shí)發(fā)出,寬度為半個(gè)時(shí)鐘C(CX):時(shí)鐘信號(hào),始終保持。在LVDS設(shè)計(jì)實(shí)現(xiàn)過程中參考XAPP233的設(shè)計(jì)方法,16位數(shù)據(jù)通過并轉(zhuǎn)串移位寄存器進(jìn)行移位處理,將偶數(shù)位鎖存于傳送時(shí)鐘的上升沿,奇數(shù)位鎖存于傳送時(shí)鐘的下降沿。其輸入/輸出采用DDR技術(shù),保證雙沿觸發(fā)。移位寄存器時(shí)鐘示意圖如圖3所示。最終輸出數(shù)據(jù)的時(shí)鐘鎖存的位置如圖4所示。LVDS電路功能框圖如圖5所示。

評(píng)論