基于Camera Link接口的圖像跟蹤系統的設計

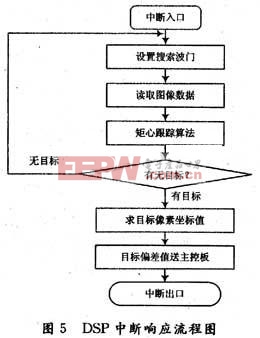

以常用的最簡單的矩心跟蹤算法為例,DSP每次響應中斷后,主要進行的工作是:首先設定搜索的波門,將波門內的數據通過DMA方式快速搬移到片內存儲器,然后用矩心跟蹤算法進行處理,直至搜索出目標后,將目標的像素的位置偏差計算出來并送給主控板。

系統要求輸出標準的PAL制式的模擬視頻,由于PAL制式視頻場頻為50 Hz,幀頻為25 Hz,所以對于前端高分辨率高幀頻的數字圖像,必須降頻輸出,且分辨率也要降低。選用專用的圖像DA芯片ADV7123,該芯片輸入位寬為10 b,可以轉換的數據速率可達240 MHz。因為標準的PAL制式視頻一幀只能顯示有效行576行,對于1 024行的數據圖像只能隔行顯示512行,且奇場256行,偶場256行。所以對于采集的圖像來說行方向上是降低了分辨率,但在列的方向上不降低分辨率。

由前面可知,由于采集顯示采用乒乓結構,但是由于顯示是隔行抽點顯示的,且顯示的頻率幀頻為25 Hz,所以在采集部分時,應當隔行取數據存儲,且每2幀才更新一次采集的數據。不像采集處理部分一樣,每幀都要更新采集的數據。

控制ADV7123的時鐘信號、復合同步信號、復合消隱信號均由FPGA產生。與電視相關的行、場同步和消隱信號正是PAL制式模擬視頻信號生成的關鍵。

FPGA 認通過對數字相機下來的80 MHz時鐘倍頻后,經過時鐘計數和邏輯組合運算獲得所需要的各種同。步時序信號。ADV7123的時鐘信號根據80 MHz時鐘先2倍頻后蔣5分頻而成,即像素時鐘頻率為32 MHz,周期為31.25 ns。生成的圖像大小為1 400×576像素,即每場圖像有288行,每行有1 400個像素點。系統采用PAL制式的隔行掃描方式,場周期時間為20 ms,行周期為64μs,所以每場包含312.5個行周期,但場消隱的高電平持續288個行周期,只要調整場消隱信號的起始位置,就很容易使視頻圖像的輸出位于屏幕的正中間。行場同步信號和消隱信號的實現思路基本上一樣:對時鐘計數,計到某一個數值時,使輸出的信號翻轉(由低電平到高電平或者由高電平到低電平),計數器的周期和翻轉的周期根據不同的參數而有所不同。由于這些時序是在FPGA中編程實現,很容易調整和修改。

至于字符疊加過程,DSP按照在圖像上實際疊加字符的位置和大小將要疊加的字符點陣寫入到FPGA片內雙口RAM中(顯示字符的地方寫二進制的1,顯示圖像的地方寫二進制的0),顯示輸出的每一幀,FPGA讀取字符疊加雙口RAM,根據其值來決定是輸出采集的圖像還是輸出疊加字符。這樣通過DSP和FPGA 的配合,可以靈活地疊加任何字符,DSP可以根據系統的任何狀態變化來改變字符疊加RAM中的值,因此保證系統具有良好的人機交互界面。

3 結語

以高性能DSP和FPGA為核心,對Camera Link接口的數字相機進行圖像采集,采用數字圖像處理技術,建立了一個實時的圖像跟蹤系統。該系統體積小、重量輕、可靠性高,具有良好的人機交互界面,已經成功地應用在實際項目中。

評論