基于Camera Link接口的圖像跟蹤系統的設計

目前使用的圖像跟蹤系統前端輸入信號一般都是PAL制式的標準全電視信號,每20 ms一場,每40 ms一幀。模擬信號經過視頻解碼器轉換成720×576大小的數字信號后,再對其中的目標進行分割、識別和跟蹤,并準確計算出目標的位置角度偏差,并傳給伺服機構。在某系統中要求能對3×3像素大小的小目標進行精確跟蹤,為了達到跟蹤精度,可以提高圖像輸入的幀頻和提高圖像輸入的分辨率,因此前端采用了 DALSA公司的一款基于Camera Link接口的數字攝像機,該相機的幀頻為100 Hz,分辨率高達1 400×1 024。這樣幀處理時間就只有10 ms,考慮到系統的實時性,我們采用了TI公司的高性能的DSP芯片TMS320C6414和高性能FPGA芯片EP2S30F672為核心的硬件處理平臺。

本文引用地址:http://www.104case.com/article/166928.htm1 系統硬件結構和工作原理

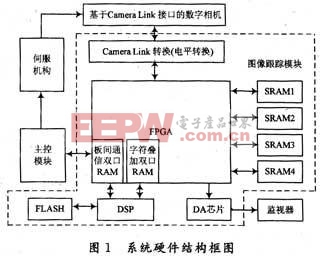

整個圖像跟蹤模塊的結構圖如圖1中虛線框所示,整個系統包括以FPGA為核心的圖像采集和預處理單元,以DSP為核心的圖像處理單元以及由FPGA控制的圖像顯示單元。

由于采集、處理、顯示均要訪問存儲器,為了降低成本,用普通的異步SRAM構成。按照功能來分可分為采集處理用SRAM組和采集顯示用SRAM組,每組分別包括兩片SRAM,其讀寫邏輯由FPGA控制,采用乒乓方式進行切換。

對于采集處理部分,第K幀時,SRAM1由FPGA控制寫入圖像數據,同時SRAM2由DSP讀數進行處理;第K+1幀時則相反,SRAM2由FPGA控制寫入圖像數據,同時SRAM1由DSP讀數進行處理。

對于采集顯示部分,第K幀時,SRAM3由FPGA控制寫入圖像數據,同時SRAM4由FPGA讀數進行顯示;第K+1幀時則相反,SRAM4由FPGA控制寫入圖像數據,同時SRAM3由FPGA讀數進行顯示。

整個系統工作過程都是這樣的:其中圖像采集單元經由差分轉換芯片后變成LVTTL信號,直接連至FPGA,由FPGA控制數字圖像的采集,進行圖像預處理后,將圖像數據存儲在SRAM中,給DSP發出中斷信號,DSP響應中斷后,從SRAM中讀取一幀圖像數據后,進行圖像分割、目標提取、目標跟蹤算法,計算出方位和高度角偏差分量,將結果通過FPGA的片內的板間通信雙口RAM傳遞給主控模塊,主控模塊再調整伺服機構保證被跟蹤的目標處于視場中心。

主控模塊還可以將系統的一些狀態變量實時的通過板間通信雙口RAM傳給DSP,DSP根據這些狀態生成需要顯示的字符,將這些字符寫入到FPGA片內字符疊加雙口RAM中。FPGA讀取顯示RAM中的圖像數據和片內字符疊加雙口RAM內的數據,在原圖上疊加十字絲和波門,以及系統的一些狀態字符信息,按照 PAL制式時序向DA芯片送視頻數據,這樣監視器就可以輸出標準的PAL制式的圖像。

2 各個單元設計

2.1 基于Camera Link接口的圖像采集和預處理單元

Camera Link是一種基于視頻應用發展而來的接口,它解決了視頻數據輸出和采集之間的速度匹配問題。Camera Link數據的傳輸率非常高,可達1 Gb/s,采用了LVDS格式,抗噪性能好。Camera Link的信號包括三個部分:串行通信部分、相機控制部分、視頻信號部分,基于Camera Link接口的圖像采集單元詳圖見圖2,每個部分采用專門的差分轉換芯片。串行通信部分則將異步串口轉換成標準的RS 232電平,這樣可以由主控機對相機的曝光時間、對比度等設置進行調節。相機控制部分包括4對差分信號,用來對相機進行控制,比如相機的外同步信號輸入控制,可以由FPGA進行控制。視頻部分的28 b LVTTL信號是關鍵控制部分,它們直接接在FPGA上,由FPGA來控制采集的時序。

評論