出租車計費器的EOA設計與實現

圖2所示為分頻得到的秒信號仿真圖,其輸入信號是整數轉換為BCD碼的轉換信號。該轉換信號頻率要求非常高,這樣可保證整數轉換BCD

碼時輸出與輸入不會產生太大的延時。仿真結果證明,該設計是正確的。

圖3給出了分頻得到的車輪走100米的輸出信號,其輸入信號為驅動車輪轉動信號。因為對不同車輪直徑,車輪走100米所需圈數不同,所以,對不同車輪進行分類討論。圖3所示的仿真波形為車輪直徑是520 mm的分頻結果。

2.3 計量模塊設計

根據出租車計費器的功能設計要求,費用的計算是按行駛的里程和等待時間來收費。當行駛里程小于3 km時,按起價計算費用;當里程大于等于3 km時每公里按2.5元計費。另外,等待累計時間大于等于4 min時,應按每分鐘1.8元計費。因此應按要求設計行駛計費使能信號clk_length和等待計費使能信號clk_time。圖4所示是這兩種信號的仿真波形圖。由圖4可知,當出租車啟動信號start為高電平有效,而等待信號stop為低電平無效時,出租車處于行駛狀態,當行駛的里程數大于等于3公里時,系統將產生有效的行駛計費使能信號;而當出租車啟動信號start為高電平有效,且等待信號stop也為高電平有效時,出租車處于等待狀態,當等待時間大于等于4分鐘時,即可產生有效的等待計費使能信號。本文引用地址:http://www.104case.com/article/166527.htm

在此要特別說明的是,因為QuartusⅡ綜合器不支持小數,因此,在設計出租車費用的時候,應將人民幣角這個單位放在個位,元放在十位。依次類推,這樣便于綜合器進行綜合。

2.4 轉換模塊的設計

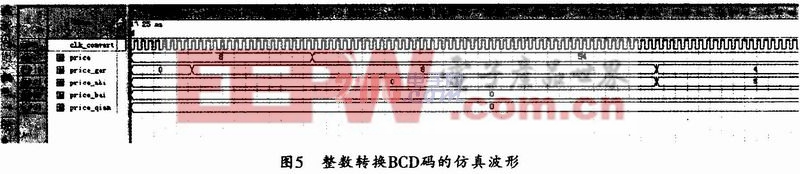

由于出租車最終的價格要由7段數碼管來顯示,而7段數碼管的輸入信號為高電平‘l’或低電平‘0’:且該設計的前面部分將價格的數據類型定義為整數,因而需要附加整數到BCD碼的轉換電路。圖5所示為整數轉換BCD碼的仿真波形。由圖5可以看出,當整數類型的價格(pri-ce)為8時,經過8個時鐘周期,BCD碼的個位就變為8;而當價格(price)為54時,經過54個時鐘周期,BCD碼的個位變為4,BCD碼的十位變為5。在此需要說明的是,圖5中的整數轉變為BCD碼需要一段時間的延時,整數數據越大,轉化輸出產生的延時就越大。為了實時的實現整數到BCD碼的轉化,需要提高轉換的時鐘信號頻率(clk_convert)。在圖2中設計的100分頻的頻率計,目的就是減小這一時間。在實際的應用中,還可以考慮提高clk_convert的頻率,設計更高的分頻倍數。

3 出租車計費器的硬件驗證

本設計選用杭州康芯電子有限公司生產的GW48EDA系統作為硬件驗證系統,同時選用Altera公司的EPlK30TCl44-3作為主控芯片。該主控芯片是一種基于查找表結構的現場可編程邏輯器件,它的基本邏輯單元是可編程的查找表。它能夠實現組合邏輯的運算,而可編程寄存器則可實現時序邏輯運算。因此,只要對出租車計費器整體設計中的輸入輸出引腳作引腳鎖定,然后重新編譯和下載,就可以進行出租車計費器的硬件驗證。實驗表明:本設計能夠實現出租車計費器的全部功能,從而證明設計是正確的。

4 結束語

本文以現場可編程邏輯器件(FPGA)為設計載體,以硬件描述語言(VHDL)為主要表達方式,以QuartusⅡ開發軟件和GW48EDA開發系統為設計工具,從而設計出具有起步定價、行駛計價和等待計價功能的出租車計費器。結果表明,本設計能夠實現所要求的全部功能。同時,因為

FPGA芯片體積小,功耗低,價格便宜,安全可靠,稍加修改就可以改變起步的價格、每公里行駛的價格和等待時間的價格等,而且維護和升級比較方便,也很容易做成ASIC芯片,因而具有較好的應用前景。

評論