基于DSP Builder的帶寬自適應全數字鎖相環的設計與實現

傳統的數字鎖相環設計在結構上希望通過采用具有低通特性的環路濾波,從而獲得穩定的振蕩控制數據。但是,在基于數字邏輯電路設計的數字鎖相環系統中,利用邏輯算法實現低通濾波是比較困難的。于是,出現了一些脈沖序列低通濾波計數電路,其中最為常見的是“N先于M”環路濾波器。這些電路通過對鑒相模塊產生的相位誤差脈沖進行計數運算,獲得可控振蕩器模塊的振蕩控制參數。脈沖序列低通濾波計

數方法是一個比較復雜的非線性處理過程,難以進行線性近似,所以無法采用系統傳遞函數分析方法確定鎖相環中的設計參數,以及進一步分析鎖相性能。在設計方法上多采用VHDL語言或者Verilog HDL語言編程完成系統設計,并利用EDA軟件對系統進行時序仿真,以驗證設計的正確性。該種設計方法就要求設計者對FPGA硬件有一定的了解,并且具有扎實的硬件描述語言編程基礎。

本文采用一種基于比例積分(PI)控制算法的環路濾波器應用于帶寬自適應的全數字鎖相環,建立了該鎖相環的數學模型,并分析該鎖相環的各項性能指標和設計參數之間的關系。利用DSP Builder直接對得到的鎖相環數學模型在Matlab/Simulink環境下進行系統級的建模,并進行計算機仿真,同時將建立的模型文件轉換成VHDL程序代碼,在QuartusⅡ軟件中進行仿真驗證,并用FPGA予以實現。

1 帶寬自適應全數字鎖相環的理論分析

1.1 基于PI控制的模擬鎖相環的理論分析

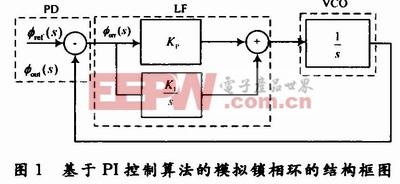

鎖相回路是一個負反饋系統,主要由鑒相器(PD)、環路濾波器(LF)和壓控振蕩器(VCO)三個部分組成。鑒相器的作用是計算輸入信號和輸出信號的之間的相位誤差。環路濾波器的主要作用是抑制噪聲及高頻分量,并且控制著環路相位校正的速度與精度。為了能夠提高鎖相系統的性能,本文采用基于PI控制算法的一階低通濾波器,即將鑒相模塊鑒別出的相位誤差大小乘以一定的比例系數而產生一個比例控制參數,同時對相位誤差大小進行積分,并在積分系數的調節下產生一個積分控制參數,最終取比例和積分控制參數的和作為該環節的控制參數。壓控振蕩器的作用就是利用輸入的電壓值控制輸出信號的頻率。設壓控振蕩器的輸入信號為V0(t),輸出信號的頻率為ω0+KV0(t),則輸出信號的相位:

![]()

式中:![]() ,則壓控振蕩器的傳遞函數為:HVCO(s)=θf(s)/V0(t)=K/s,可以看出壓控振蕩器相當于一個固有積分環節。在該設計中取壓控振蕩器的增益K=1,則通過以上的分析可得基于PI控制算法的模擬鎖相環結構框圖如圖1所示。

,則壓控振蕩器的傳遞函數為:HVCO(s)=θf(s)/V0(t)=K/s,可以看出壓控振蕩器相當于一個固有積分環節。在該設計中取壓控振蕩器的增益K=1,則通過以上的分析可得基于PI控制算法的模擬鎖相環結構框圖如圖1所示。

由圖1可以得出,該鎖相回路的閉環傳遞函數為:

![]()

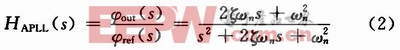

不難看出該系統是一個典型的二階系統,那么二階模擬鎖相環的閉環傳遞函數可表示為:

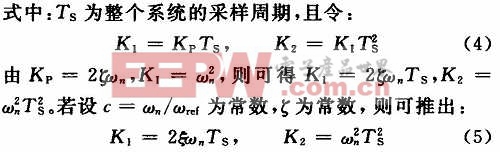

式中:Kp和Kl分別為比例系數和積分系數,取![]() 為系統的自然頻率;ζ為系統的阻尼系數。

為系統的自然頻率;ζ為系統的阻尼系數。

1.2 帶寬自適應全數字鎖相環的理論分析

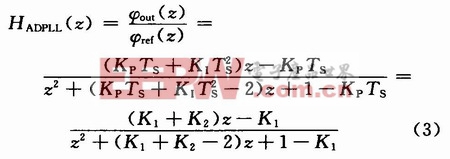

對上述模擬鎖相環的s域傳遞函數進行離散化處理,采用脈沖響應不變法即可得到全數字鎖相環回路的閉環傳遞函數為:

于是可以得到基于參數K1和K2的全數字鎖相環的結構圖如圖2所示。

評論