基于PCIe總線的航空視頻采集記錄系統的設計

2.3 視頻數據回放

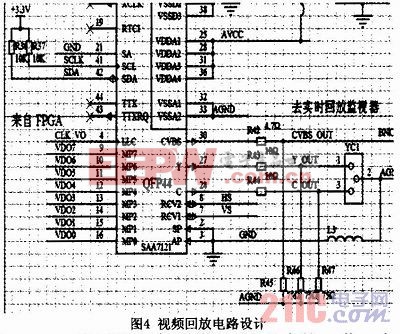

視頻回放是方便飛行員能夠實時監控訓練和試驗的情況。系統采用Philips公司的SAA7121視頻編碼器,將FPGA處理后的視頻數據轉換為PAL制的綜合視頻,送給飛行員面前的監視器進行顯示。如圖4所示。本文引用地址:http://www.104case.com/article/165890.htm

SAA7121需要進行初始化配置后才能工作,初始化通過設置編碼器的寄存器,配置其工作模式。初始化要通過I2C總線完成,系統的I2C總線接口由FPGA實現。同步時鐘CLK VO和8-bit并行視頻數據都是由FPGA解碼處理后傳輸過來的。編碼器的工作頻率為27MHz,FPGA解碼后的視頻數據經過SAA7121編碼器的綜合視頻信號CVBS送給監視器。同時也設計了一個備用的YC分量視頻接口。

2.4 視頻傳輸

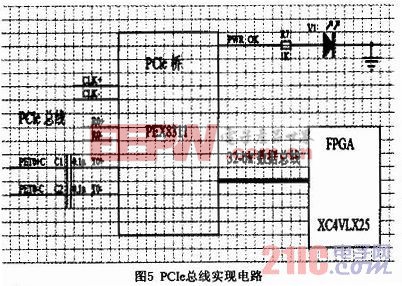

采集的視頻數據經過FPGA解碼處理后需要通過PCIe總線傳輸給嵌入式CPU以便于實時壓縮存儲。實現高速的PCIe總線是海量數據傳輸的關鍵。數據傳輸總線技術是不斷更新發展的過程。在數據通訊的起初階段,串行通訊因為信號簡單、實現方便而應用廣泛,占有統治地位,例如RS422串行通訊,盡管速率不高,目前仍然很有生命力。為解決串行通訊的瓶頸問題,開始采用并行傳輸總線,并行通訊的速率取決于時鐘頻率和數據寬度。目前最流行33MHz/32bit的PCI總線,峰值傳輸速率可達132Mbps。當繼續提高時鐘頻率時,并行通訊總線的數據寬度卻成為繼續提高速率的障礙。由于極高頻下的線路串擾和反饋,難以保證多路并行總線信號數據同步的一致性,數據通訊的傳輸技術從并行回歸到串行,并行雙向的PCI總線發展為串行單向的PCIe總線。速率高達2.5Gbps的PCIe總線有三對差分信號,即同步時鐘CLK+/CLK-、接收信號R+/R-和發送信號T+/T-。PCIe總線設計電路如圖5所示。

在PCIe這種高速信號傳輸總線中,數據不是直接通過信號導線的電壓信號,而是通過高頻耦合方式傳輸的。圖5中的C1、C2就是發送方的耦合電容,應盡量靠近橋片。每一對差分信號都應該有耦合電容,圖5中時鐘和接收信號對的耦合電容,隱含在PCIe的主控方。

評論