如何利用FPGA降低手持設(shè)備MPU的功耗

消費類手持設(shè)備市場正呈跳躍式發(fā)展。便攜式產(chǎn)品處理能力不斷增加,所支持的應(yīng)用越來越多;產(chǎn)品更新?lián)Q代速度加快,新產(chǎn)品必須滿足上市時間要求,以便獲得最大的市場機會;產(chǎn)品生命周期的縮短要求縮短開發(fā)周期,同時更加強調(diào)可復(fù)用性和可重復(fù)編程能力。新興手持設(shè)備市場還有一個有趣的趨勢,即一個系列中的每種設(shè)備的出貨量越來越少,但系列設(shè)備間的定制功能卻越來越多,進而有效提升了產(chǎn)品的總出貨量。這樣,關(guān)鍵挑戰(zhàn)就變成了如何開發(fā)一個可廣泛復(fù)用同時又可定制的系統(tǒng)。

本文引用地址:http://www.104case.com/article/165671.htm為應(yīng)對上述挑戰(zhàn),越來越多的設(shè)計人員開始使用FPGA進行手持產(chǎn)品的開發(fā)。FPGA的功能日益強大和豐富,而門數(shù)、面積和頻率也在不斷增加。FPGA的開發(fā)和周轉(zhuǎn)時間要比定制ASIC短得多,可重復(fù)編程的額外優(yōu)勢使得FPGA成為手持嵌入式系統(tǒng)領(lǐng)域中頗具吸引力的解決方案。在基于ASIC或FPGA的設(shè)計中,設(shè)計人員必須認真考慮某些性能標準,他們面臨的挑戰(zhàn)主要體現(xiàn)在面積、速度和功耗方面。

與ASIC一樣,供應(yīng)商在FPGA設(shè)計中也需要應(yīng)對面積和速度的挑戰(zhàn)。隨著門數(shù)不斷增加,F(xiàn)PGA需要更大的面積和尺寸來適應(yīng)更多的應(yīng)用,設(shè)計工具需要采用更好的算法以便更有效地利用面積。不斷演進的FPGA技術(shù)也給設(shè)計人員帶來一系列新的挑戰(zhàn),電源利用率就是其中之一,這對于為手持或便攜式設(shè)備設(shè)計基于FPGA的嵌入式系統(tǒng)來說是急需解決的問題。

嵌入式系統(tǒng)中的FPGA

典型的嵌入式系統(tǒng)由處理器、存儲器、包括USB、SPI、I2C在內(nèi)的標準接口以及液晶顯示器、音頻輸出等外設(shè)組成。設(shè)備的核心仍是處理器和處理器接口,它們通過板載連線連接到各個外設(shè)。系統(tǒng)性能主要取決于處理器性能,而處理器通常具有非常標準的架構(gòu),因而不容易定制。

有時處理器可能忙于處理來自低速外設(shè)的信息,雖然在這種情況下處理器使用率可能達到100%,但并不是在做以微處理器為中心的事務(wù),而是工作在特別低的性能水平。不管其內(nèi)核頻率是多少,微處理器必須等待來自低速時鐘的數(shù)據(jù)。這也會導(dǎo)致較高的功耗,因為處理器的利用率是100%。其結(jié)果將縮短電池壽命,并且需要更大的散熱器或風扇進行冷卻,最終影響整個系統(tǒng)的可靠性。

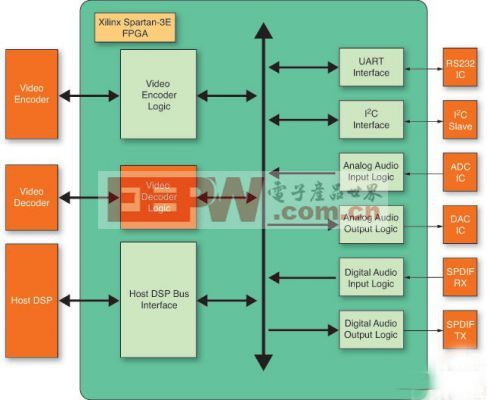

于是,F(xiàn)PGA在這方面開始發(fā)揮重要作用,因為它們能從處理器卸載許多外設(shè)交互任務(wù)。如圖1所示,利用標準千兆TCP/IP網(wǎng)絡(luò)實現(xiàn)的未壓縮音視頻數(shù)據(jù)流的嵌入式分布系統(tǒng)。它有一個專用DSP處理器,這個處理器通過一個標準總線接口與賽靈思的FPGA相接,F(xiàn)PGA再連接到各個低速外設(shè)。

圖1:用于音頻/視頻分布系統(tǒng)的FPGA架構(gòu)

作為啟動開發(fā)套件,這個FPGA通過I2S接口連接12位的PCM音頻輸入和12位的PCM音頻輸出;它還連接視頻編碼器和解碼器,并與I2C從器件和RS232器件進行通信;連接到FPGA的通用I/O很少。與處理器相連的標準總線工作在高速的66MHz,而音頻外設(shè)工作在低速的1.182MHz;UART和I2C串行接口分別工作在56.6kHz和100kHz。由于數(shù)據(jù)傳輸發(fā)生在多個時鐘域,因而只有處理器能配置數(shù)據(jù)流。

在這種情況下,處理器不再與低速外設(shè)交互,而由FPGA從低速的PCM ADC音頻器件讀取數(shù)據(jù),并將數(shù)據(jù)存放在FPGA的內(nèi)部緩存中。處理器可以周期性地從這個緩存讀取數(shù)據(jù),或者當緩存中有足夠數(shù)據(jù)時,由FPGA向處理器發(fā)送一個中斷。這樣,處理器就有更多的時間執(zhí)行以處理器為中心的必要工作,在空閑時則進入睡眠模式。

功耗問題

在電池供電的嵌入式系統(tǒng)中,節(jié)能是最重要的考慮因素。功耗可以被分成三大類:啟動功耗、靜態(tài)功耗和動態(tài)功耗。設(shè)計人員無法控制啟動功耗,而啟動功耗在決定電源選型中扮演著重要的角色。大多數(shù)最大電流值指的就是這個階段所達到的值。但靜態(tài)功耗和動態(tài)功耗是兩個不同的領(lǐng)域,通過合理的規(guī)劃和以下正確的指導(dǎo)原則,使用FPGA的嵌入式設(shè)計人員可以在功耗優(yōu)化方面作出顯著改進。

靜態(tài)功耗是指系統(tǒng)不工作時仍有電流流過元件時產(chǎn)生的功耗,一般由器件偏置電流和漏電流引起。靜態(tài)功耗也取決于工作電壓,降低工作電壓可以降低靜態(tài)功耗,但這個策略并不總是掌握在設(shè)計人員手中。設(shè)計人員能做的是定義合理的架構(gòu),在這種架構(gòu)下需要使用的資源最少,同時盡可能使用資源共享,并以最高效的方式使用FPGA模塊。

減少靜態(tài)功耗的另外一種技術(shù)是在設(shè)計周期早期進行功耗預(yù)估,改變拓撲或使用不同的IP模塊。例如,賽靈思的xPower Estimator工具這時就非常有用,它能很早知道設(shè)計是否滿足功耗預(yù)算。早期階段的功耗預(yù)估也許不完全準確,但作為指導(dǎo)工具確實很有幫助。

動態(tài)功耗是由于FPGA門的一些行為(比如信號開關(guān))引起的,當兩個門暫時導(dǎo)通時,將產(chǎn)生電流流動和電容。信號開關(guān)的速度決定了功耗的大小。影響動態(tài)功耗的另外一個因素是電路內(nèi)部結(jié)構(gòu)中形成的固有電容。動態(tài)功耗是時鐘頻率、正在開關(guān)的門數(shù)量和這些門開關(guān)速率的函數(shù)。門扇出和走線上的電容負載會增加動態(tài)功耗,并且功耗值正比于電容、電壓和頻率平方的乘積。

設(shè)計人員對這種功耗具有最大的控制能力,他們可以利用許多技術(shù)實現(xiàn)動態(tài)功耗的最大改善。降低信號開關(guān)頻率可以使功耗呈指數(shù)式下降。正如圖1所示,用于UART的控制邏輯、奇偶校驗或幀超限錯誤都發(fā)生在速度較低的時鐘域。即使門數(shù)沒有減少,功耗也會下降。設(shè)計人員還可以通過降低整體工作頻率(如果可行的話)來減小動態(tài)功耗。例如,在完成可行性和性能分析后,設(shè)計人員決定上述設(shè)計不僅能工作在133MHz,也能工作在66MHz。DSP支持這兩種速率,而減小電壓也有助于降低功耗。

另外一種技術(shù)是減少處于工作模式的有效門數(shù)。有時某部分邏輯雖然在開機時被打開和配置,但實際上不要求做任何事情。例如,模擬音頻捕獲單元處于工作狀態(tài),設(shè)備卻不在執(zhí)行任何數(shù)字SPDIF音頻捕獲。在這種情況下,一般的數(shù)字SPDIF音頻捕獲電路仍將執(zhí)行數(shù)據(jù)采樣、雙相解碼等工作,因而無謂地浪費功率。如果禁用整個數(shù)字SPDIF音頻捕獲電路,使電路中不發(fā)生任何信號開關(guān)動作,那么動態(tài)功耗將會顯著降低。

評論