基于AIS的船舶避碰系統研究

3.2 DSP和FPGA的接口設計

比較Altera公司的多個系列的FPGA產品,本設計選取CycloneⅡ系列的芯片EP2C35F672。它主要具有以下特性:嵌入式存儲資源支持各種存儲器應用和數字信號處理(DSP)實施的要求,引腳數量充裕有160個,可提供100個I/O用戶引腳,且I/O具有三態緩沖、總線狀態保持等功能,該芯片由128 MB FLASH內存和8 MB SSRAM存儲區和兩個串口。它可以滿足本系統所需的數據采集控制和串行口復用等功能。接口電路如圖3所示。

在上述設計中AIS信息的串口直接接到DSP芯片上,是為了避免直接應用多串行口中斷共享方式可能會不可靠。原因是假如在服務串行口A時上一次檢測過的串行口B發生了中斷,此時中斷服務程序如果直接退出,則中斷B就未被服務。這種情況下,CPU可能會再次進入中斷服務程序,多次進出中斷必然造成處理器資源的浪費。更糟糕的是退出中斷服務程序時,由于DSP中斷標志位已經被清除且DSP中斷引腳保持高電平,此時中斷就不會再被標志,造成中斷死鎖導致外部中斷根本無法繼續工作。為確保DSP芯片及時接收到AIS信息,為AIS單獨留下專用串口。

3.3 DSP和FPGA與其他外圍電路的接口設計

船舶避碰系統中設計了基于同一片FPGA上的液晶顯示接口和鍵盤接口,使避碰系統具有更強的功能。鍵盤接口利用FPGA內的硬件資源設計,在不影響DSP進行船舶避碰算法運算的條件下,用于船舶避碰系統的調試和控制。

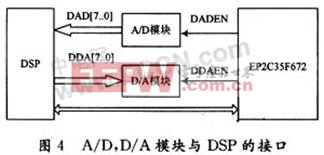

同時完成了A/D、D/A模塊的接口設計。模擬信號經過前置濾波、放大,再通過多路模擬開關和A/D轉換器轉換成數字信號進入FPGA,A/D、D/A模塊與DSP的接口電路如圖4所示。

4 結 語

本文研究的內容為基于AIS的船舶避碰系統,涉及到信息的解碼過程,利用DSP作為系統的微處理器和FPGA作為接口的擴展與協調,根據接收的信息,進行船舶避碰算法的運算。

評論