CMOS圖像傳感器IBIS5-B-1300的驅動時序設計

2.1 現場可編程門陣列FPGA

隨著集成電路的發展,大規模可編程邏輯器件廣泛用于電路設計領域,它具有功耗低,可靠性高的特點,同時大大減小了電路板的尺寸。FPGA的內部結構決定了FPGA在時序設計方面的優越性。該設計選用Xilinx公司的Spartan3系列FPGA芯片XC3$50作為硬件設計平臺。Spar-tan3基于VirtexⅡFPGA架構,采用90 nm技術,8層金屬工藝,內嵌硬核乘法器和數字時鐘管理模塊。從結構上看,它將邏輯、存儲器、數字運算、數字處理器、I/O以及系統管理資源完美地結合在一起,使之具有更高層次、更廣泛的應用。

2.2 控制時序的設計

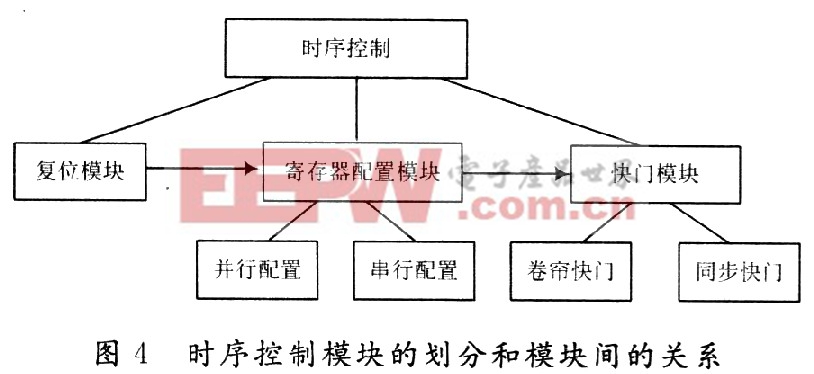

該設計采用VHDL硬件描述語言,根據自頂向下的設計方法,將時序控制部分分為三個模塊:復位模塊、寄存器配置模塊和快門模塊。由于寄存器有兩種配置方式,快門模式也有兩種,因而后兩部分都可以再細分為兩個小模塊。三個大的模塊有嚴格的先后關系,必須在前一模塊已完成后,才可開始后一模塊。圖4顯示模塊的劃分及其關系。本文引用地址:http://www.104case.com/article/163108.htm

復位模塊是用來產生圖像傳感器所需的SYS_RE_SET信號,使傳感器正常復位,內部寄存器清零,為寄存器的配置做好準備。

寄存器配置模塊是用來配置圖像傳感器內部的12個寄存器,提供傳感器工作所需的參數和方式。其中,參數有積分時間、積分方式(單斜率或多斜率)、X序列發生器的時鐘間隔、SS序列發生器的時鐘間隔、亞采樣方式、開窗位置及大小等。

快門模塊用于產生傳感器工作所需的一些控制信號,針對快門方式的不同給出所需的時序控制信號。在同步快門的設計中,該設計采用單斜率積分,在此設計基礎上多斜率積分容易實現。

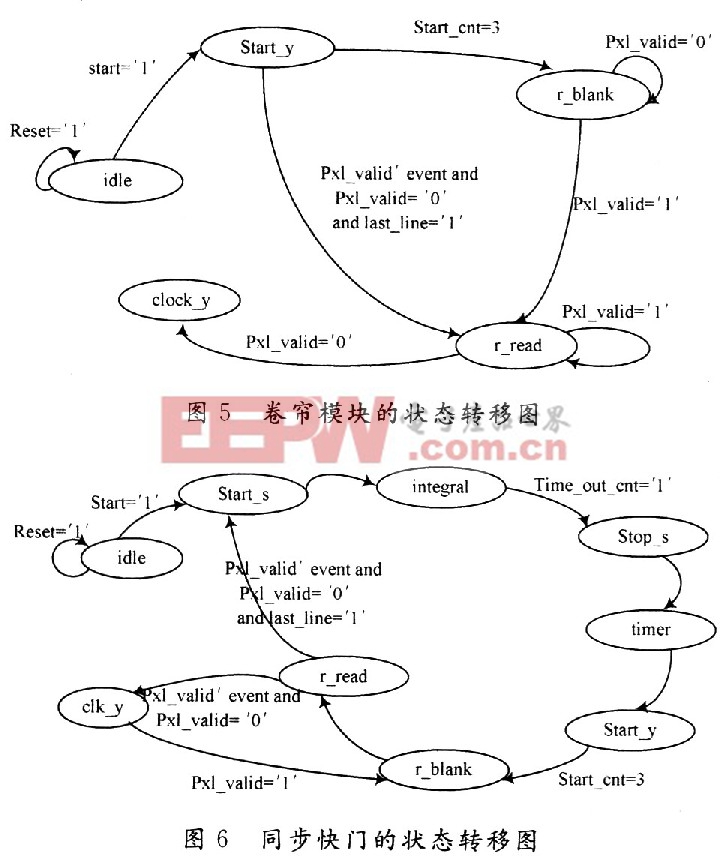

該設計采用VHDL對各模塊時序進行編程。其中,快門模塊使用狀態機來實現各狀態之間的轉換(圖5顯示了卷簾模塊的狀態轉移圖,圖6顯示了同步快門的狀態轉移圖)。全局時鐘和ADC時鐘采用DCM即數字時鐘管理單元來實現。

3 實驗結果

3.1 仿真結果

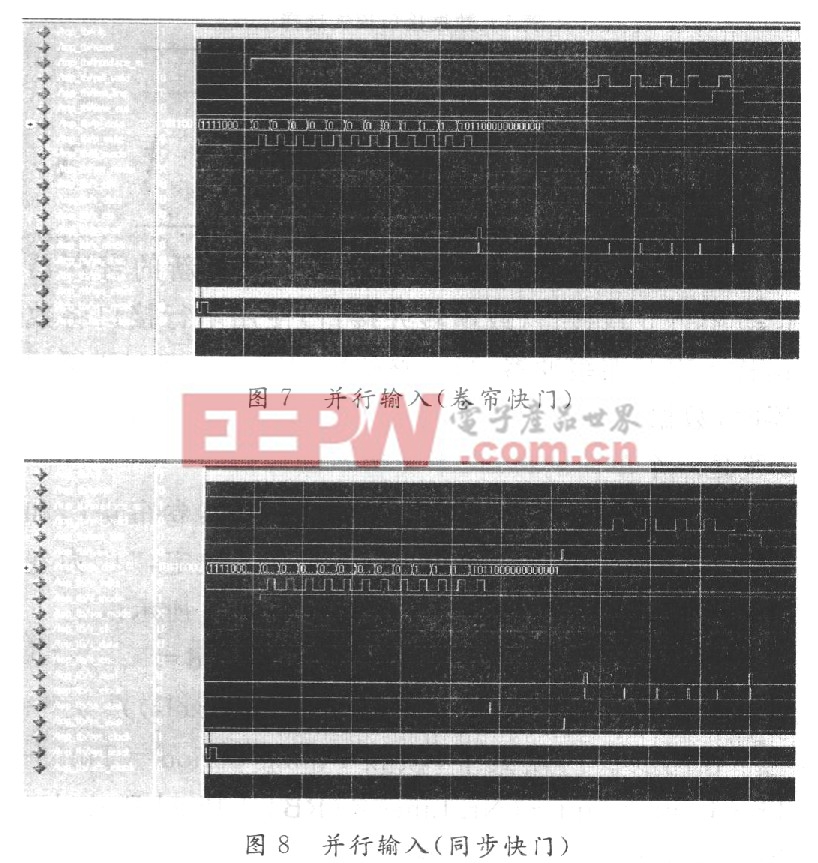

時序控制電路設計完畢后,需要對各部分進行功能仿真、邏輯綜合以及綜合后仿真,最后對整個系統進行綜合、布局布線,完成時序仿真。對各模塊編程并仿真通過后,將各模塊加載到主函數top中,采用并行的寄存器配置方式,對卷簾和同步兩種快門方式進行仿真,在Modelsim中的仿真結果如圖7,圖8所示。

3.2 成像結果

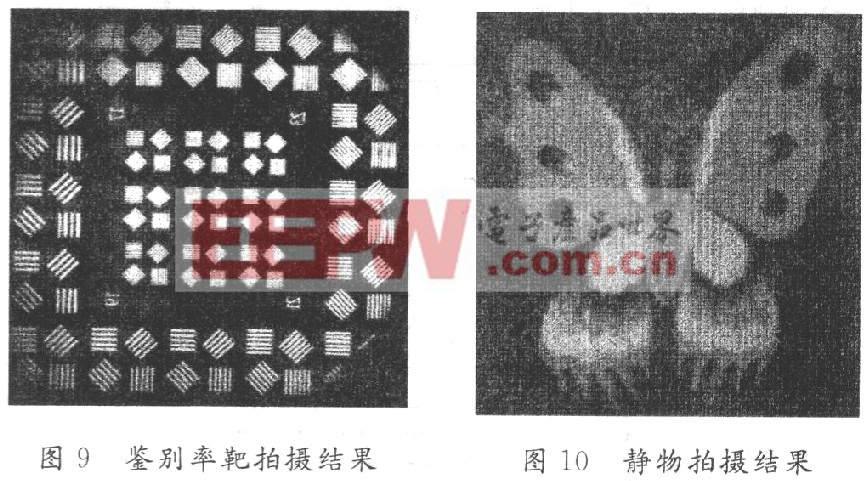

將此驅動時序應用于相機系統,在全幀輸出模式(1 280×1 024)下,對鑒別率靶和靜物進行拍攝,實驗結果如圖9,圖10所示。由所拍攝結果可以看出,圖像清晰穩定,無明顯變形,CMOS圖像傳感器滿足了成像的需求。

4 結語

圖像傳感器驅動時序的正確與否對其能否正常工作起著決定性的作用。本文在分析CMOS圖像傳感器IBIS5-B-1300工作時序的基礎上,設計了兩種寄存器配置方案和兩種快門方式,并用FPGA內嵌的數字時鐘管理單元(DCM)完成了系統時鐘和ACD時鐘的設計。實驗結果表明,所設計的驅動時序可以滿足該圖像傳感器的驅動要求。

評論