電子產品面板控制芯片的后端設計

2.3 布局

布局就是放置電子產品面板控制芯片中各個標準單元位置的過程,在布局期間要求優化一個特定的目標函數,這個目標函數通常包括時序、連線長度、擁塞等。本設計采用時序驅動布局將關鍵路徑上的單元放得很近,以縮短連線長度來減小關鍵路徑時延。但為了減少擁塞度,要把連線均勻地分布在版圖上,以避免局部擁塞的現象,因此對布局時的最大密度設置為50%。通過對時序分析和阻塞分析,可知這種做法既達到時序收斂,又不會出現擁塞,布局效果良好。

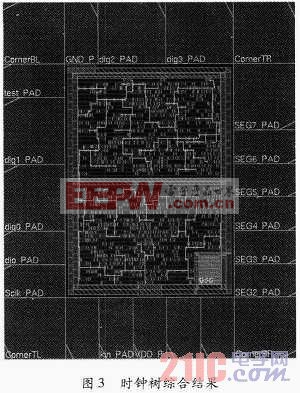

2.4 時鐘樹綜合

由于同步設計電路中所有的操作都需要時鐘控制來實現同步,而時鐘網絡在所有信號網絡中負載最大、走線最長、要求最苛刻,因此時鐘樹綜合的質量直接影響芯片的性能。時鐘樹綜合的目的在于控制時鐘傳播延遲、時鐘偏移和跳變時間。較大的時鐘延遲對解決電路的建立時間問題不利,較大的時鐘偏移會增加寄存器鎖存不穩定數據的幾率,而控制好跳變時間有利于優化時鐘樹的功耗。本設計先采用在自動CTS模式下,根據時鐘樹規格文件中的時序約束自動決定級別數和緩沖器數,然后根據設計中的具體情況用手動方式修改級別數、緩沖器類型以及所連接的寄存器,以達到盡可能好的效果。通過比較時鐘樹綜合報告文件可知,在自動模式下,時鐘偏移為0.13 ns,通過手動修改后時鐘偏移為0.078 ns,時鐘樹綜合結果顯示,如圖3所示。

2.5布線

SOC Encounter在布線時分為兩個階段完成:預布線和詳細布線。預布線時布線工具把整個芯片劃分為多個較小的區域,布線器只是估算各個小區域的信號之間最短的連線長度,并以此來計算連線延遲和每個區域的布線擁塞程度,這個階段并沒有生成真正的版圖連線。詳細布線時考慮信號完整性和時序驅動,同時可修復天線效應、串擾影響和設計規則違反。詳細布線工具尋找并修復短路和開路的線,同時完成布線后優化。在詳細布線時,Routing Track定義,布圖規劃,setNanoRouteMode命令參數設置的沖突會引起線的開路。出現開路情況后使用verifyTracks命令可以診斷標準單元的線的開路問題,能報告出在Blockage內部引腳的距離太遠,引腳未對齊,引腳在Stripes下面等問題。通過對報告分析,了解原因后進行布局調整直到解決問題。

2.6 可制造性設計

可制造性設計包括消除天線效應(NEC0.35CZ6H工藝不需要)、加Core填充單元(FILL1,FILL2)、優化接觸孔、加金屬填充滿足金屬密度要求。

默認情況下是使用單孔進行上下層之間的連接,在空間允許的情況下可使用雙孔或多孔進行連接,使用雙孔或多孔的目的是減少過孔電阻、減少電遷移引起的失效,有利于時序收斂和提高良率。布線工具會利用:Multiple-cut Vias或Fat Vias替換掉信號過孔達到優化過孔的目的。詳細布線時利用插入Multi-Cut Via或Fat Vias修復串擾。

版圖是由一行行等高Row組成,由于Row放置標準單元的利用率不可能達到100%,因此在Row中標準單元之間可能會有大小不等的間隙,這些間隙若不用填充單元進行填充,則在物理驗證工具進行設計規則檢查時會產生大量DRC違規,解決辦法是加Core填充單元(FILL2,FIL-L1)。

根據CZ6H工藝中的金屬密度填充規則對所有金屬層加入考慮時序的金屬填充,這樣可盡量避免在時鐘和信號線周圍加入金屬填充,而更多的是加在電源和地線周圍。

評論