采用QCM傳感器的生物芯片檢測電路的原理設(shè)計

軟件設(shè)計

本系統(tǒng)中ALTERA公司可編程邏輯器件EPM7128的內(nèi)核程序采用Verilog HDL硬件描述語言編寫,使用MAX+plusII10.1編譯系統(tǒng)或Quartus II 4.2編譯系統(tǒng)編譯,設(shè)計實現(xiàn)了分頻、頻率計數(shù)、數(shù)據(jù)選擇等功能。51單片機AT89S52用C語言和匯編語言混合編程,使用Keil C51編譯系統(tǒng)編譯。

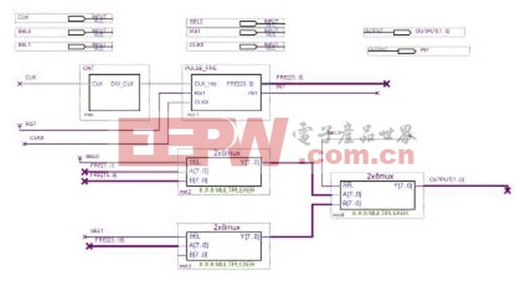

1、可編程邏輯器件EPM7128的頂層電路

頂層電路如圖4所示,由分頻模塊、計數(shù)模塊、數(shù)據(jù)選擇模塊組成,分頻模塊和計數(shù)模塊采用Verilog HDL硬件描述語言編寫,數(shù)據(jù)選擇模塊用圖形輸入方式。12M的振蕩信號送到EPM7128的CLK端,經(jīng)過分頻模塊后變成10Hz的頻率信號給計數(shù)模塊提供基準時基。AT89S52給EPM7128的RST端提供復(fù)位RST信號,使EPM7128復(fù)位,開始記錄差頻器送到EPM7128的CLKX1端的頻率信號。記時時間到,EPM7128的輸出端INT發(fā)出中斷信號,通知單片機接收數(shù)據(jù)。由于計數(shù)模塊的計時器是32位的,因此通過3個8位的二選一數(shù)據(jù)選擇器,在單片機給出的SEL0~SEL2片選信號控制下,分時選擇從EPM7128的輸出端OUTPUT7~OUTPUT0輸出的8位數(shù)據(jù)信號到AT89S52的P0數(shù)據(jù)口。

圖4 可編程邏輯器件EPM7128的頂層電路

2、可編程邏輯器件EPM7128的分頻模塊

分頻模塊的目的是將可編程邏輯器件EPM7128的83腳輸入的12M頻率信號,分頻成10Hz頻率信號給計數(shù)模塊做基準時鐘,即計時時間是100ms。

3、可編程邏輯器件EPM7128的計數(shù)模塊 由分頻模塊分頻后的10Hz信號送到計數(shù)模塊,它通過門控電路,加到可以控制開、閉時間的閘門上。被測脈沖加到計數(shù)模塊中閘門的輸入端,開始測頻時,先將計數(shù)器置0,待門控信號到來后,打開閘門,允許被測脈沖通過,計數(shù)器開始計數(shù),直到門控信號結(jié)束,閘門關(guān)閉,停止計數(shù)。因此,當門控信號的周期為1s時,在閘門開通時間1s通過閘門的被測脈沖個數(shù)即為該被測信號的頻率,為了使上位機獲得更多的數(shù)據(jù)和精度,使門控信號的周期為0.1s。

以下是可編程邏輯器件EPM7128的計數(shù)模塊的程序部分代碼:

always @ (posedge CLK_1hz or negedge RST)

begin

if (!RST)

begin

CNT_EN=0;

LOAD=1;

end

else

begin

CNT_EN=~CNT_EN;

LOAD=~CNT_EN;

end

end

assign CNT_CLR=~(~CLK_1hzLOAD);

ssign INT=LOAD; //使用LOAD的上升沿使單片機中斷。

DIY機械鍵盤相關(guān)社區(qū):機械鍵盤DIY

評論