采用可定制微控制器來優化算法的設計

Atmel公司的CAP可定制微控制器為這種挑戰提出了一種可行的解決方案。CAP是一塊基于微控制器的系統級芯片,能提供基本的處理能力,以及高密度的金屬可編程(MP)數字邏輯塊,這些塊可以進行個性化,提供類似于DSP或其它專用的功能執行硬件。CAP同時具有合理的開發周期與具有吸引力的單位批量價格的成本好處。專用CAP的開發流程包括基于開發板的仿真步驟,這個開發板使用高密度的FPGA來仿真算法執行功能,這種功能隨后硬化在金屬可編程模塊中。

本文引用地址:http://www.104case.com/article/162127.htm 從全球定位系統到音視頻媒體流處理,這些應用都需要實時地執行復雜的算法,很多這些算法都需要遵從定期更新的行業標準。工程師開發這些應用面臨的挑戰是在單位成本、外形尺寸和功耗,以及嚴格的成本和開發時間約束下,優化這些算法的執行,這些產品通常是大批量生產。終端用戶產品必須能以合理的成本對處理算法進行升級。

硬件/軟件的權衡

最佳算法實現的基本經驗是,硬件是為了實現更高的性能,軟件是為了實現靈活性。實際上,這種經驗很難以實際應用。硬件的選擇受限于微控制器內核的基本算法函數,以及DSP內核的乘法/累加和線性函數處理,雖然FPGA所具有更高靈活度,但其缺點是外形尺寸、功耗以及批量時的單位成本。可選的標準單元ASIC可以提供更高的性能,但是因為開發時間和成本而常常不能采用。

軟件被移植到選用于硬件實現的微控制器或者MCU/DSP組合上。一旦硬件/軟件的劃分完成以后,再要做出改變將非常難,而且非常耗時,除非是基于FPGA進行批量生產。通常,只有在應用開發的最后階段軟件才可以運行于目標硬件,并確定處理算法的實現是否為最佳。

CAP算法實現流程

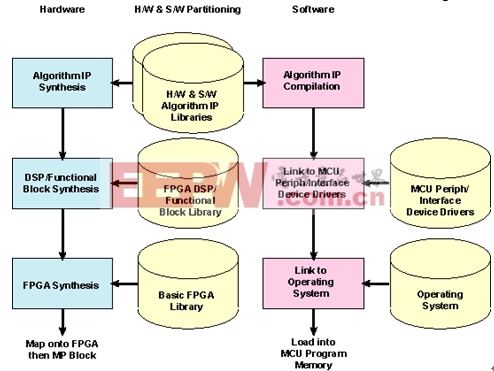

CAP使應用開發工程師能獲得FPGA和ASIC兩者的優點。CAP應用開發周期的第一階段使用基于FPGA的庫和工具來實現算法的初步硬件/軟件劃分,然后將基于硬件的功能映射到類似于DSP的架構,或者在FPGA中實現的其他處理單元。同時,微控制器對基于軟件的算法處理進行編譯,微控制器可以在其地址空間中看到FPGA/MP模塊,并采用分布式DMA架構優化功能和存儲器模塊之間的數據流。圖1顯示了硬件/軟件劃分以及使用IP模塊庫來實現算法的整個步驟,IP模塊包含硬件模塊以及他們相關的軟件驅動程序。

圖1:CAP算法硬件/軟件劃分和實現流程。

在硬件上,首先利用IP庫或FPGA提供商的工具來對算法模塊進行綜合;然后這些再與來自FPGA提供商的庫的DSP或類似功能模塊進行綜合;最后的步驟是將這些高層的結構映射到基本的FPGA架構上,以在CAP開發板上配置FPGA。

在軟件上,算法所要求的IP模塊被編譯,然后與Atmel公司的低層器件驅動程序庫鏈接起來,這些器件驅動程序處理多個外設阻止的操作以及CAP SoC的外部接口。如果有要求,該代碼可以鏈接到操作系統、用戶界面以及頂層控制模塊來實現這個系統的運行。全部的代碼組被加載到用于微控制器內核的程序存儲器中,微控制器內核是CAP的中心架構單元。

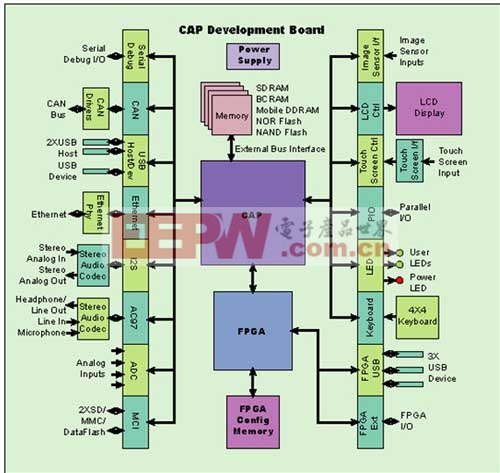

CAP開發板的基本架構如圖2所示。設備的固定部分是在CAP芯片中,它以標準的微控制器加片上存儲器、外設和接口實現的,所有這些在圖中顯示為外部連接。各種存儲器都可以連接到外部總線接口(EBI)。

圖2:CAP開發板。

開發中算法的硬件部分通過其配置存儲器映射到FPGA中,軟件被加載到微控制器所選擇的外部或內部程序存儲器中。這樣,所配置的開發板以接近運行速度仿真最后的CAP器件,包括非常難以進行仿真的多任務處理進程間通信和中斷。這種仿真步驟使算法實現能在真實使用條件下徹底調試。它還使可以利用衡量標準來確定最初的硬件/軟件劃分以及之后不同模塊的綜合/編譯是否是最優化的。如果要求改進,這些可以使用前面介紹的相同設計流程來實現,除了延長開發時間外,并不會增加額外的成本。可以通過硬件/軟件的分割以及硬件/軟件實現的多次設計迭代來獲得最佳的設計。

CAP金屬編程和制造流程

一旦所開發的設備的功能被固定下來,對FPGA進行編程所使用的最終RTL代碼被映射到(由Ateml公司或授權的第三方設計公司)金屬層來對CAP金屬可編程模塊進行個性化。苛刻的布局后仿真能確保金屬編程CAP的功能與仿真版本的功能相同。

原型很快地生產出來,應用開發人員可以對設備的硬件/軟件功能進行最后的驗證,特別是用來檢查算法是否是最佳的。在最糟糕的情況下,如果原型并不令人滿意,從仿真階段的額外返工成本和時間是合理的,遠遠低于標準單元ASIC的完全掩模替代的成本和時間。在原型得到批準后,便開始個性化CAP設備的批量生產,使用原型生產的相同流程。

設計師根據現場反饋,并根據任何數據處理算法的升級,基于在金屬編程之前開發板的最終FPGA配置的修改,從而可以快速開發出基于CAP的設備改進版本,并比最初的版本成本更低。

本文結論

Atmel公司的CAP可定制化微控制器解決了復雜算法優化的挑戰。特別是,它使得算法實現的硬件/軟件分割能在接近運算速度和實際使用條件下進行仿真。然后,所選擇的實現被硬化到金屬可編程模塊中,這個模塊能提供最佳的性能和功耗,并且非常具有吸引力的批量單位成本。 在不需要額外開發成本的情況下可以對算法實現多次迭代設計,以確定哪一個是最優的。

評論